mrinalmani

Advanced Member level 1

- Joined

- Oct 7, 2011

- Messages

- 463

- Helped

- 60

- Reputation

- 121

- Reaction score

- 58

- Trophy points

- 1,318

- Location

- Delhi, India

- Activity points

- 5,285

Hi

A 3.3V PWM input is stepped up to 12V using a BJT. The BJT has a speed up capacitor of 50pF. The output from the BJT is fed to an inverted push-pull stage. (Inverted as in the P MOSFET is at the bottom and N at the top)

The problem is that soon after the BJT switches ON, it immediately switches OFF for a few nano seconds and then switches ON again.

1. When the speed up capacitor is removed, there is no such problem.

2. Or when load capacitor is reduced to a small value, again the problem dissapears.

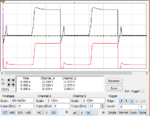

See the waveform of switching.

Black: Out1

Red: Out2

Why is the BJT turning off momentarily?

Thank you!

A 3.3V PWM input is stepped up to 12V using a BJT. The BJT has a speed up capacitor of 50pF. The output from the BJT is fed to an inverted push-pull stage. (Inverted as in the P MOSFET is at the bottom and N at the top)

The problem is that soon after the BJT switches ON, it immediately switches OFF for a few nano seconds and then switches ON again.

1. When the speed up capacitor is removed, there is no such problem.

2. Or when load capacitor is reduced to a small value, again the problem dissapears.

See the waveform of switching.

Black: Out1

Red: Out2

Why is the BJT turning off momentarily?

Thank you!