Porsche

Member level 1

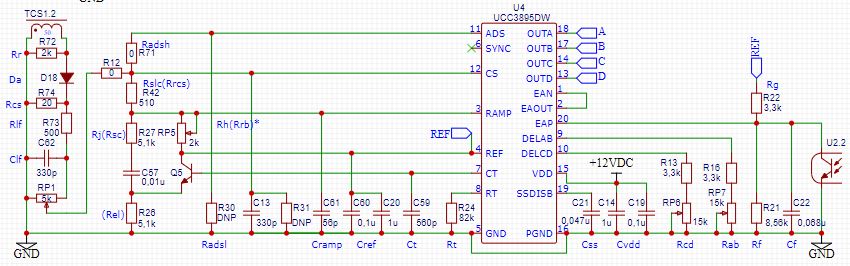

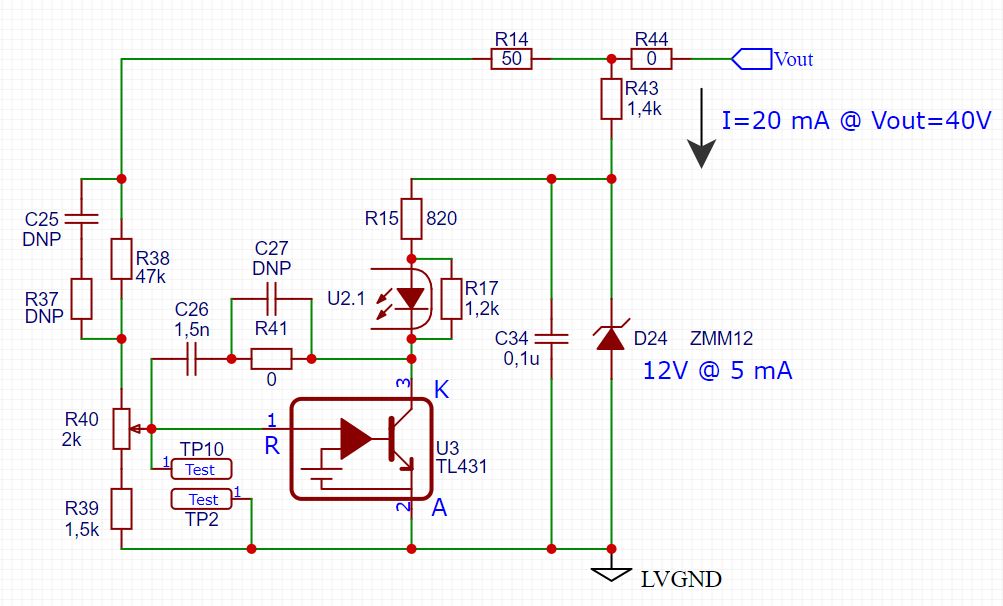

Hello everyone! I got some issues with PSFB output voltage stabilization. I used UCC3895 datasheet as reference for moderator action: removed link to external file server.

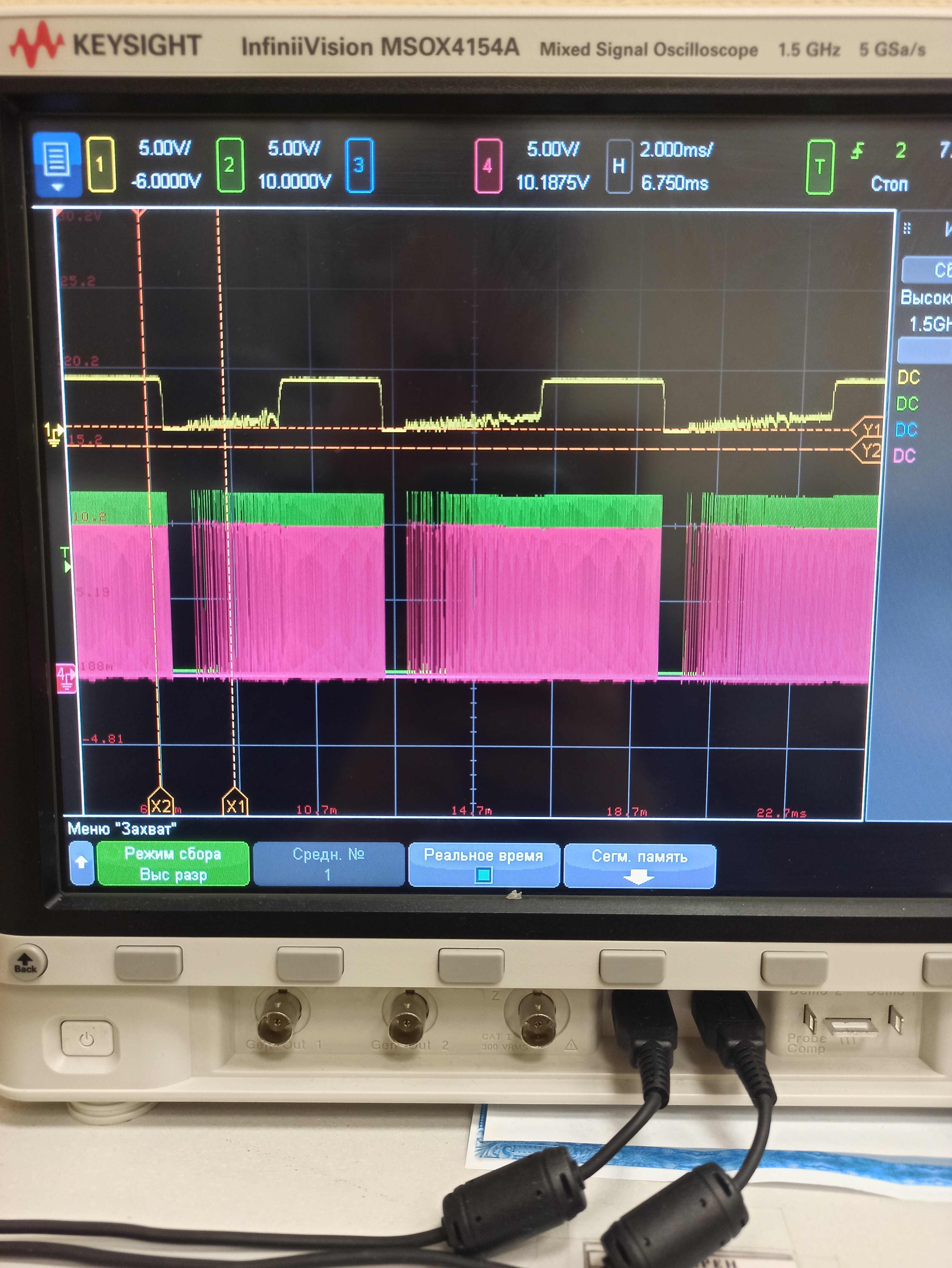

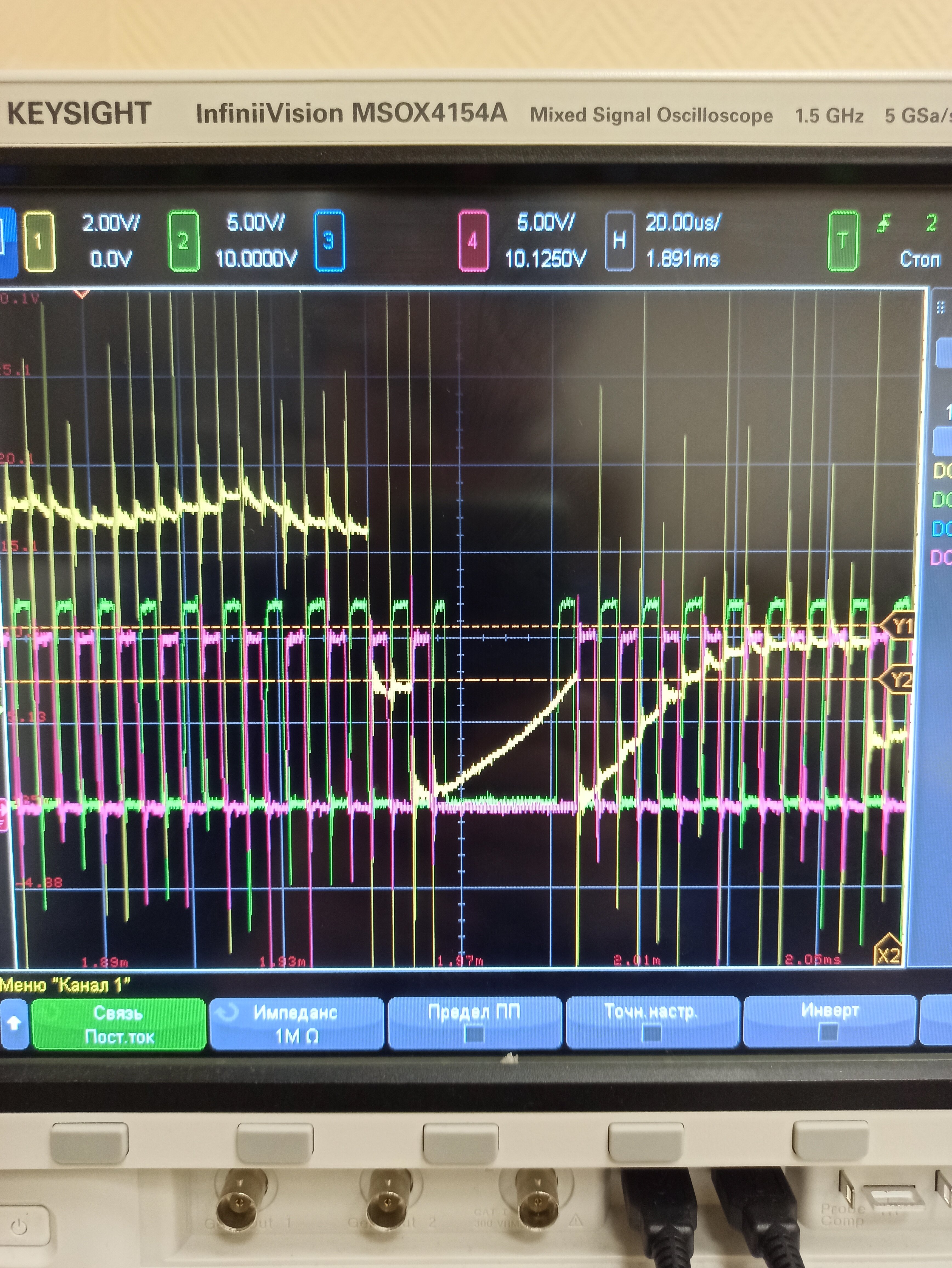

The problem occurs when converter starts to stabilize output voltage. The output voltage is somehow stable, but stabilization occurs at audible frequency so I can hear crackle and unpleasant noise. Waveforms shows that stabilization occurs in a few beats then EAP voltage hits no-load comparator threshold and disables the output. Then EAP voltage rises, PWM enables and everything is repeated again. I tried to put C26 in wide capacitance range (100p up to 0.1u) and this is didn't help much. Did anybody faced a similar problem, what is proper way to make it stable?

Please look at the waveforms and schematic. Yellow – voltage on EAP pin, green and pink is Vgs voltage of QA and QD mosfets. Load is ~6R:

The problem occurs when converter starts to stabilize output voltage. The output voltage is somehow stable, but stabilization occurs at audible frequency so I can hear crackle and unpleasant noise. Waveforms shows that stabilization occurs in a few beats then EAP voltage hits no-load comparator threshold and disables the output. Then EAP voltage rises, PWM enables and everything is repeated again. I tried to put C26 in wide capacitance range (100p up to 0.1u) and this is didn't help much. Did anybody faced a similar problem, what is proper way to make it stable?

Please look at the waveforms and schematic. Yellow – voltage on EAP pin, green and pink is Vgs voltage of QA and QD mosfets. Load is ~6R:

Last edited by a moderator: