Porsche

Member level 1

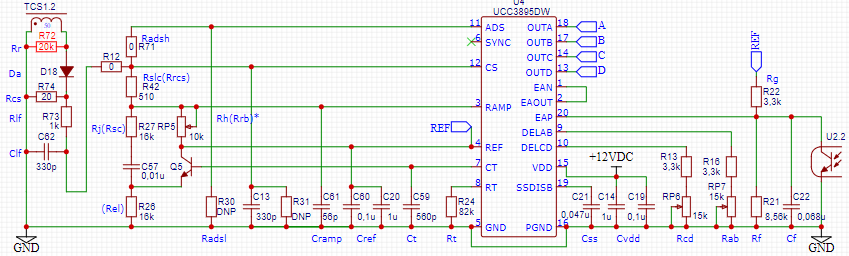

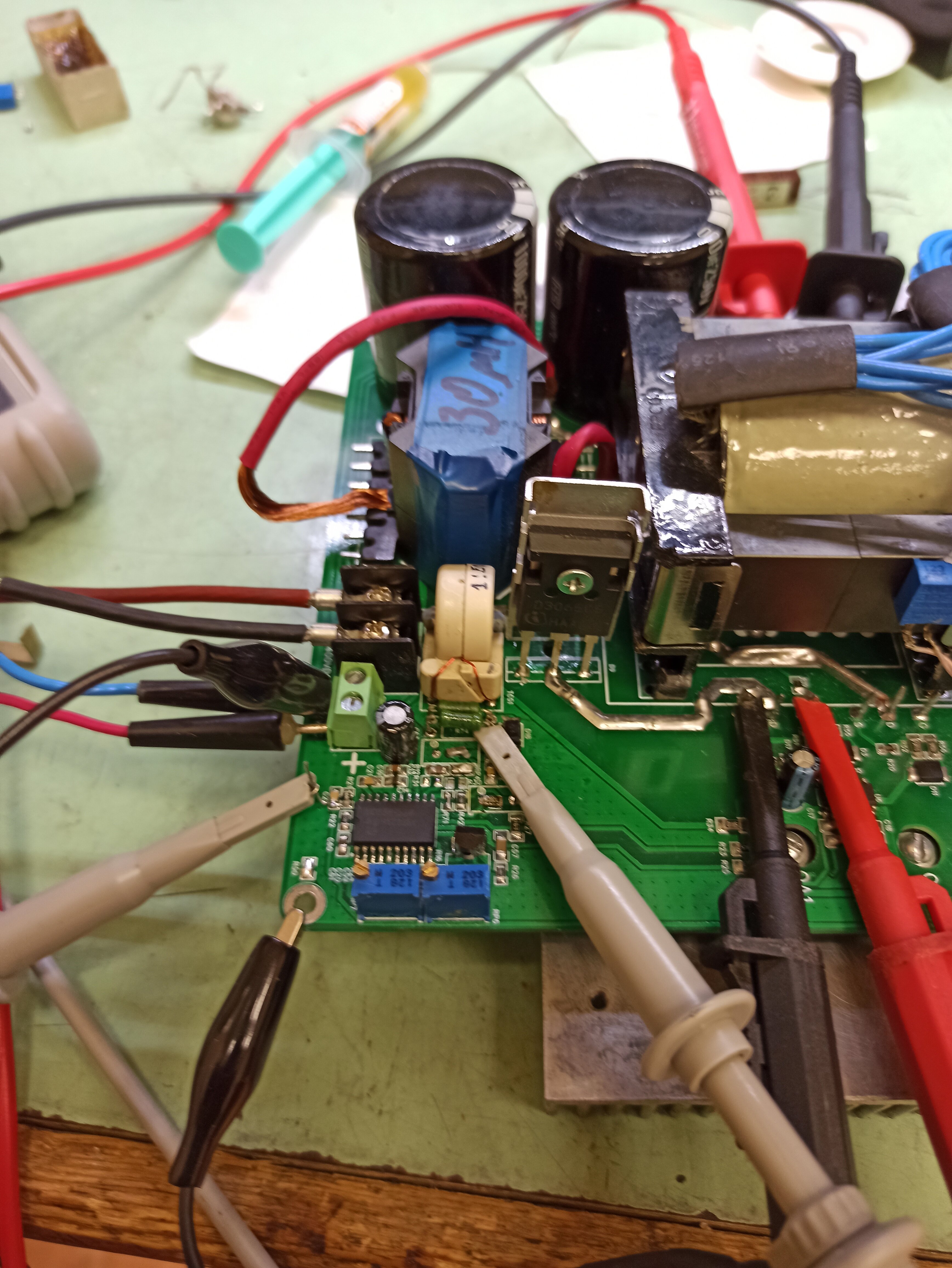

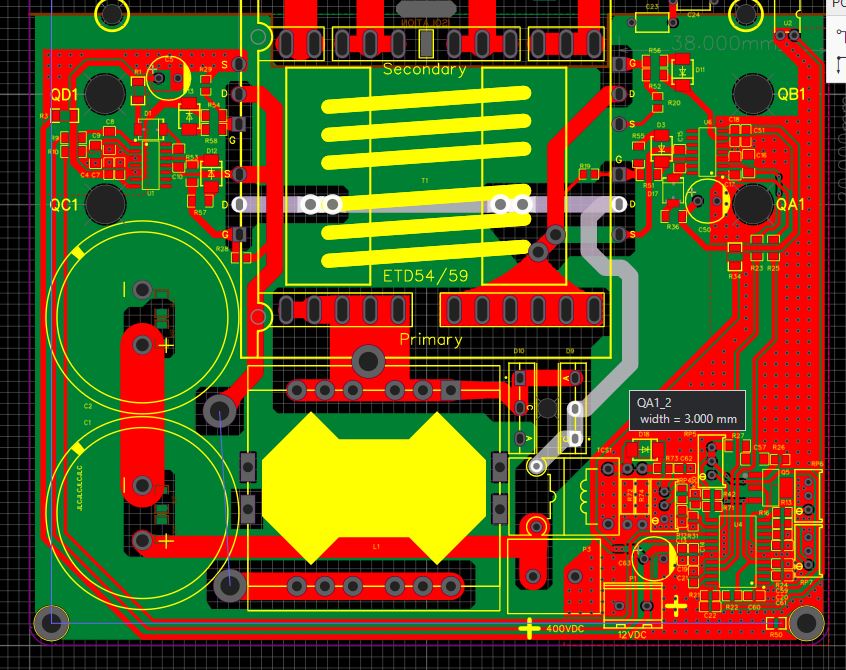

Hello everyone! I am working on PSFB based on UCC3895. **broken link removed** is practically similar to the DS’s one. Before turning it on at full power i decided to look at current waveform, so i put a load resistor at the output of the converter and have disabled feedback loop. So PWM controller provides 100% phase shift at any condition.

First, I turned on PWM controller and then I started to raise HV voltage slow. As I have some load resistor at the output, I expected to saw current waveform at Rcs also rises as I raising HV voltage. But instead, I saw that current waveform is not a right shape and it has low amplitude. What could be the reason?

My current sensor has a 1:50 transfer ratio, the secondary inductance is 3,4 mH.

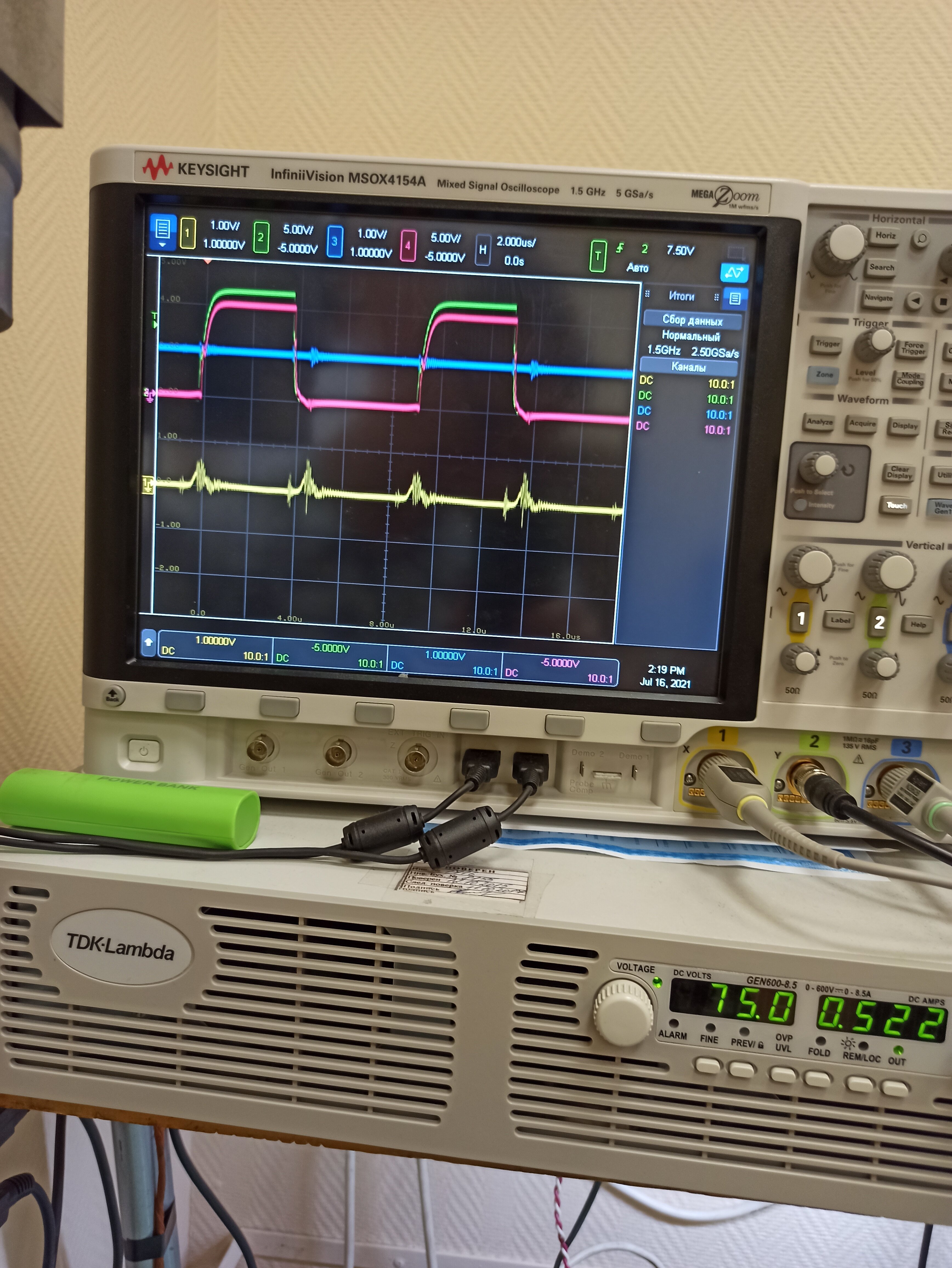

Here what i got:

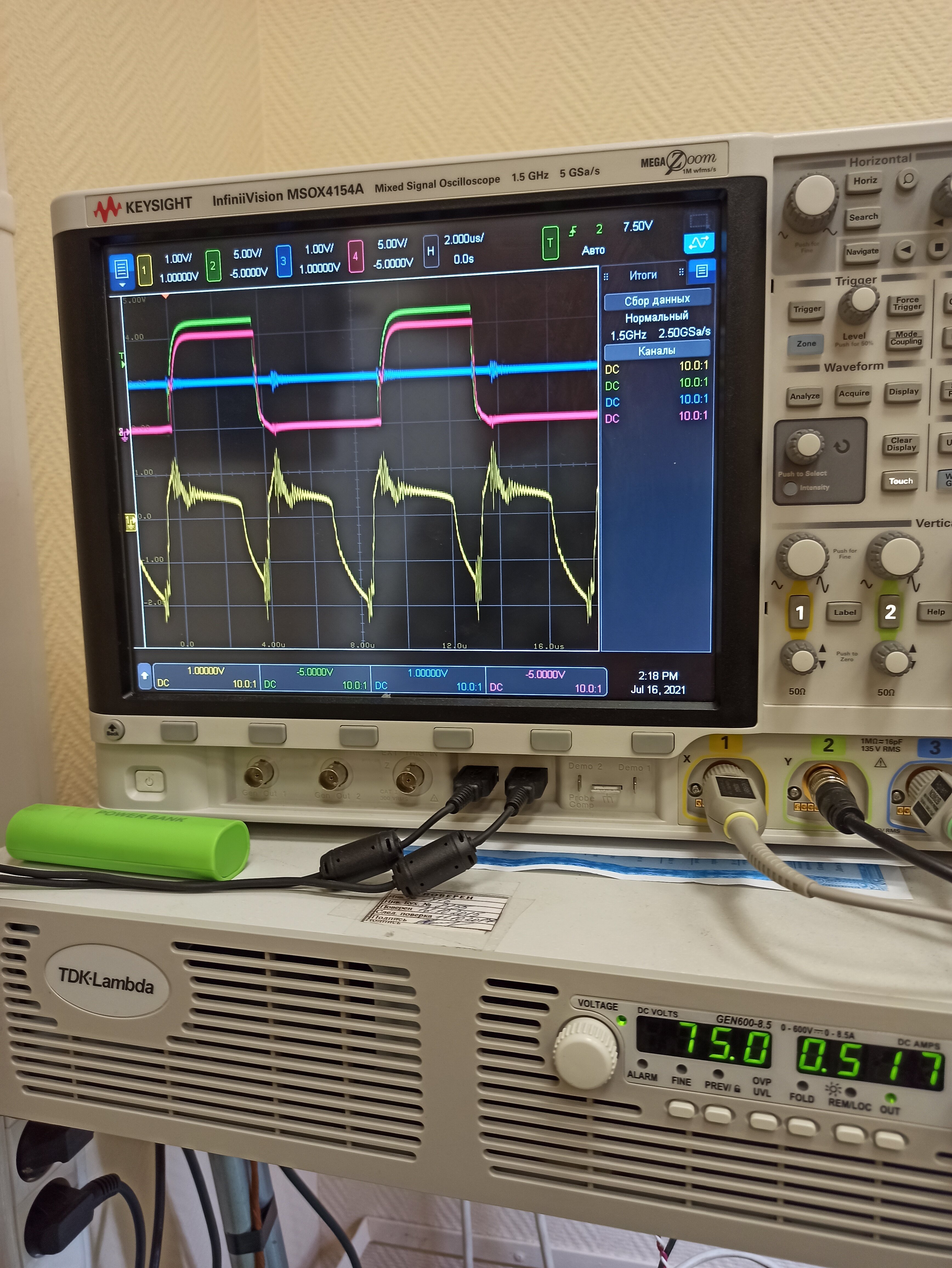

1. Input current 0.522A Yellow - measured across Rcs (20R); green and red at QA and QD gates.

1. Input current 0.522A Yellow - measured across Rcs (20R); green and red at QA and QD gates.

2. Input current 0.517A Yellow - measured across Rr (20K)

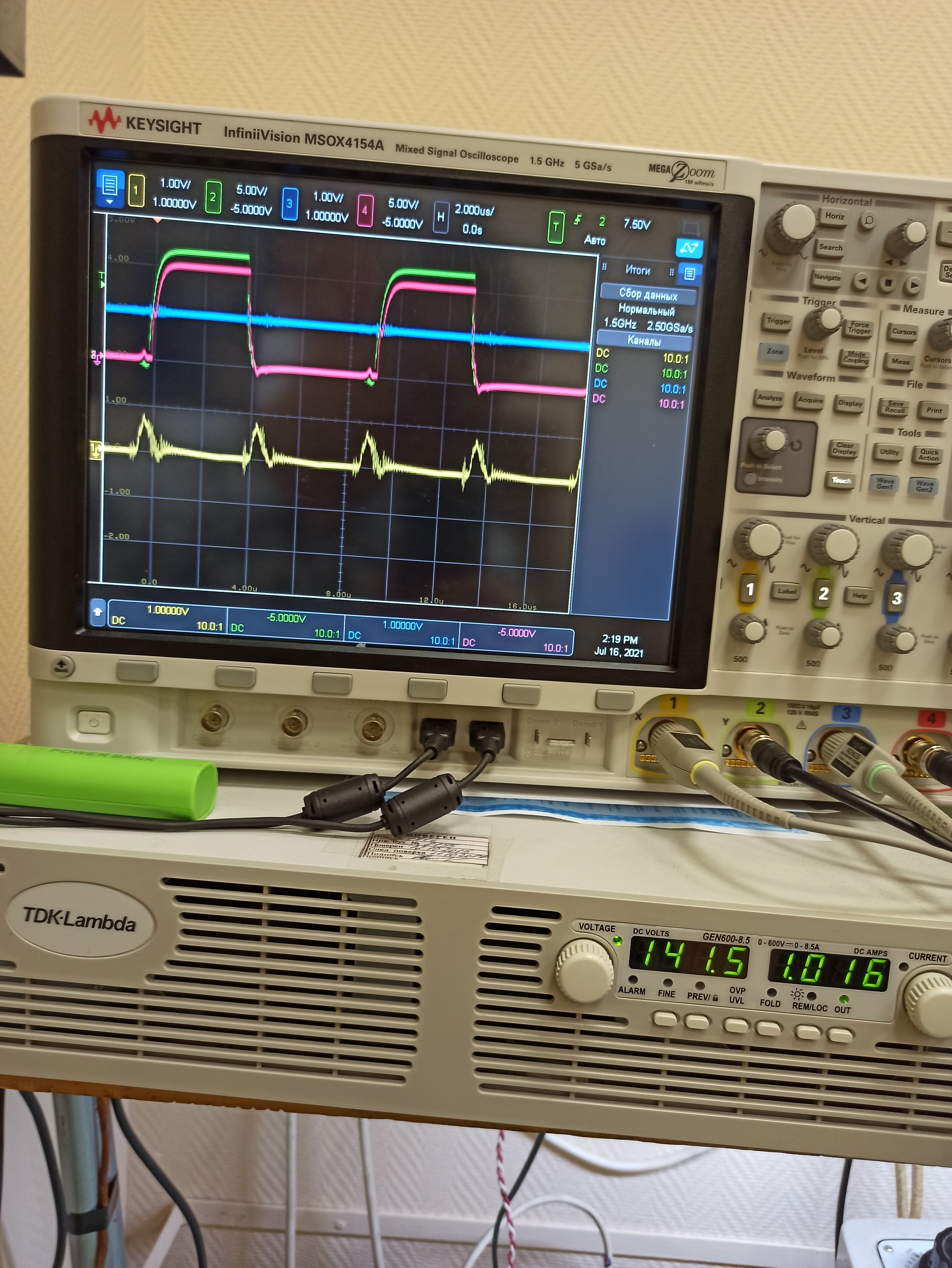

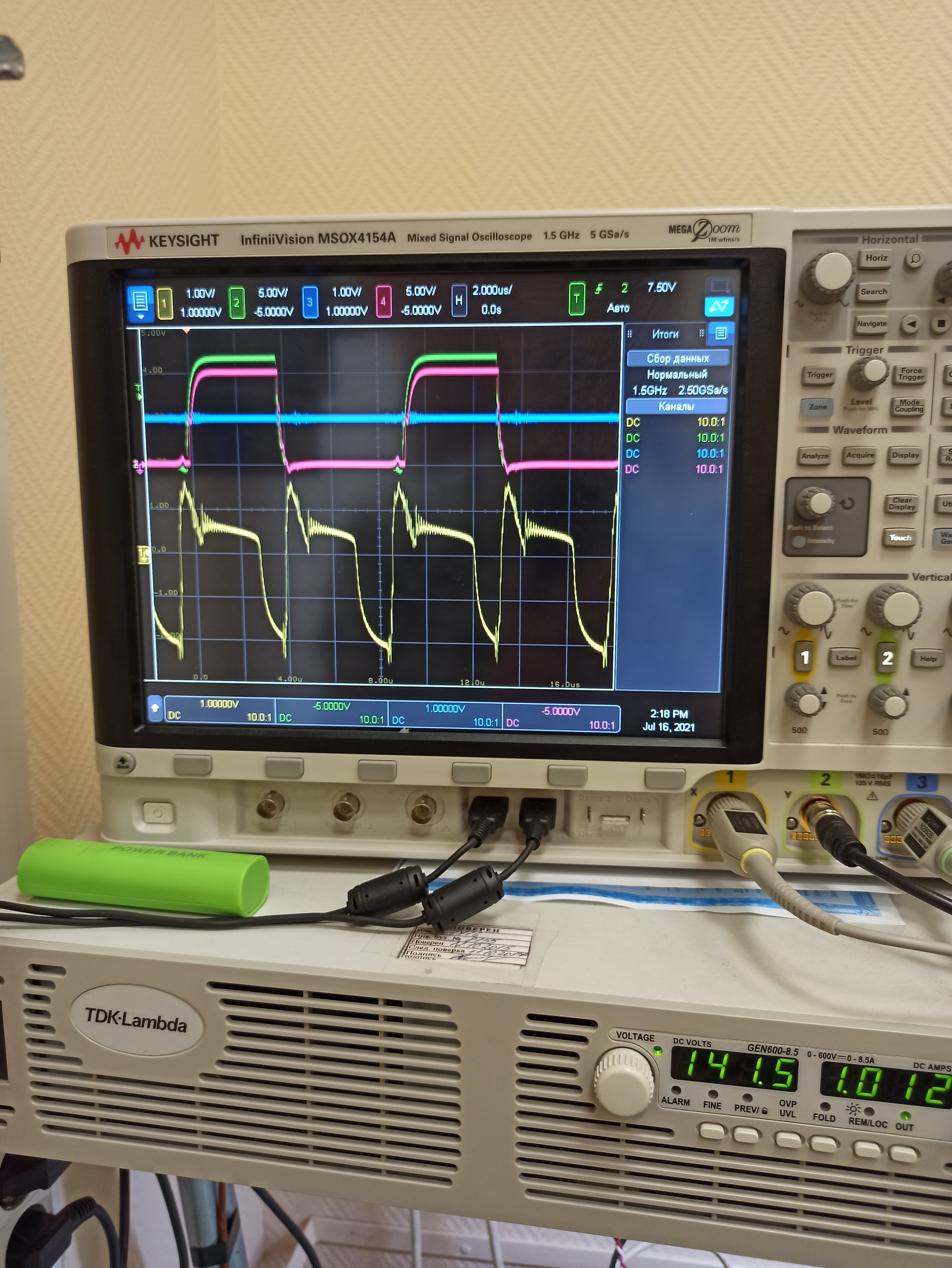

1. Input current 1.016A Yellow - measured across Rcs (20R); green and red at QA and QD gates.

1. Input current 1.016A Yellow - measured across Rcs (20R); green and red at QA and QD gates.

2. Input current 1.012A Yellow - measured across Rr (20K)

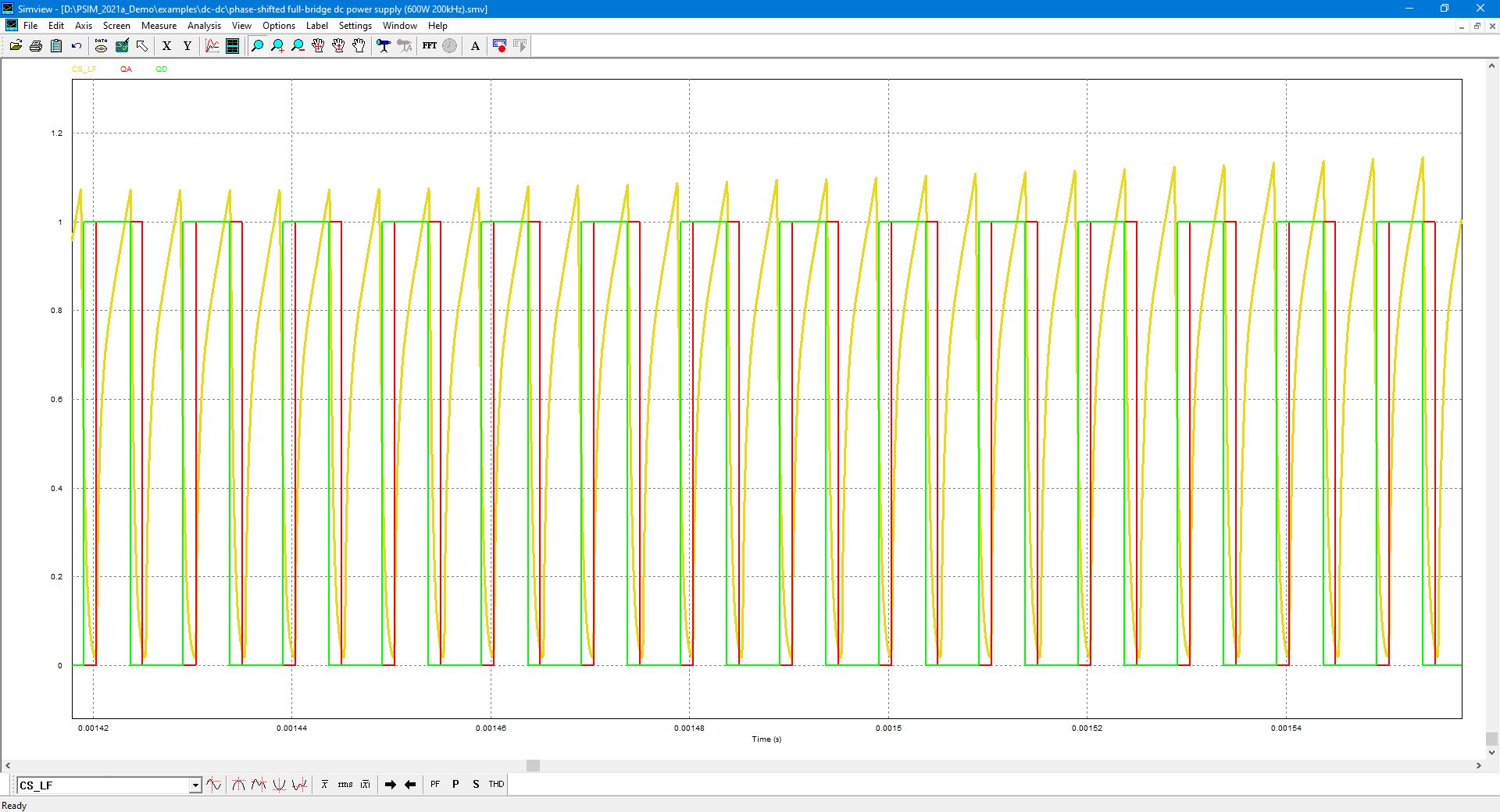

Simulation shows current waveform should look more like sawtooth.

Simulation shows current waveform should look more like sawtooth.

P.S. I am sorry for my grammar. I hope it's not so terrible.

P.S. I am sorry for my grammar. I hope it's not so terrible.

First, I turned on PWM controller and then I started to raise HV voltage slow. As I have some load resistor at the output, I expected to saw current waveform at Rcs also rises as I raising HV voltage. But instead, I saw that current waveform is not a right shape and it has low amplitude. What could be the reason?

My current sensor has a 1:50 transfer ratio, the secondary inductance is 3,4 mH.

Here what i got:

2. Input current 0.517A Yellow - measured across Rr (20K)

2. Input current 1.012A Yellow - measured across Rr (20K)