Mysterion

Newbie

Hello everyone

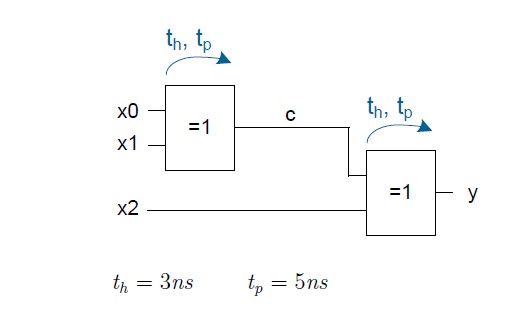

I need to modify the XOR operations used in the parity calculation in such a way that the XOR gates described are each supplemented by a hold time and the propagation delay and use the circuit diagram as a guide.

For the duration of the hold time, the signal used should be assigned the value "X" (invalid) in the VHDL description, and after the delay time, the new valid signal value. Note that signal delays are non-synthesisable constructs.

I'm just confused about the delay implementation. Should X(0)/X(1) be stable for 5ns or 8ns ? and X(2) for 3ns or 5ns ?

That's the code I wrote, but like I said, I'm not sure about the delay implementation and would appreciate some guidance.

Thank you in advance for your help !

I need to modify the XOR operations used in the parity calculation in such a way that the XOR gates described are each supplemented by a hold time and the propagation delay and use the circuit diagram as a guide.

For the duration of the hold time, the signal used should be assigned the value "X" (invalid) in the VHDL description, and after the delay time, the new valid signal value. Note that signal delays are non-synthesisable constructs.

I'm just confused about the delay implementation. Should X(0)/X(1) be stable for 5ns or 8ns ? and X(2) for 3ns or 5ns ?

That's the code I wrote, but like I said, I'm not sure about the delay implementation and would appreciate some guidance.

Code:

library ieee;

use ieee.std_logic_1164.all;

entity parity_gen is

port( x : in std_logic_vector (2 downto 0);

y : out std_logic_vector (3 downto 0)

);

end parity_gen;

architecture sig_handling of parity_gen is

signal peven: std_logic;

begin

process(peven, x)

begin

peven <= x(0) xor x(1) xor x(2) after 10 ns;

if (x(0)'stable(8 ns) and x(1)'stable(8 ns) and x(2)'stable(3 ns)) then

y <= peven & x ;

else

y <= 'X' & x after 10 ns;

end if;

end process;

end sig_handling;

Last edited by a moderator: