Ravinder487

Full Member level 3

- Joined

- Jul 9, 2010

- Messages

- 169

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,296

- Location

- Bangalore, India

- Activity points

- 2,469

Hi all,

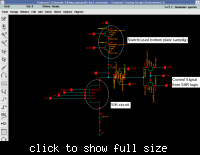

I'm facing one serious problem with Charge redistribution DAC

During sampling phase top switch(circled in fig) tries to discharge output of DAC to ground,but in sampling phase all the capacitors are charged to input voltage hence bottom plates of all capacitors track the input signal. Due to this all the top plates(shorted together) are following input signal and aren't getting ground.

I hope you all understood my problem. Please help me solving this issue. What type of switch do I need to use.

I'm facing one serious problem with Charge redistribution DAC

During sampling phase top switch(circled in fig) tries to discharge output of DAC to ground,but in sampling phase all the capacitors are charged to input voltage hence bottom plates of all capacitors track the input signal. Due to this all the top plates(shorted together) are following input signal and aren't getting ground.

I hope you all understood my problem. Please help me solving this issue. What type of switch do I need to use.

Last edited: