vasusathiyam

Newbie level 6

- Joined

- Jul 29, 2011

- Messages

- 13

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Location

- Thirunelveli, Tamilnadu

- Activity points

- 1,354

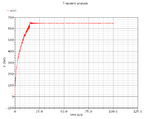

Here i attached the control voltage to the VCO of PLL.

From this i know my PLL(2nd order PLL) is going to lock that is the input of the VCO well known from PSS analysis.

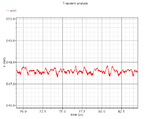

But i got some oscillation while locking the phase of the signal(2nd wave)

(Measured by delta cursor i got 500MHz but in calculator not coming)

Can anyone explain the reason where is the problem?