Fayaz143

Newbie level 6

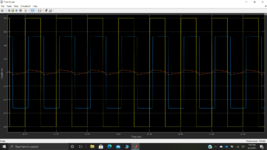

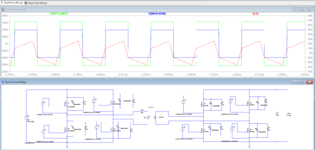

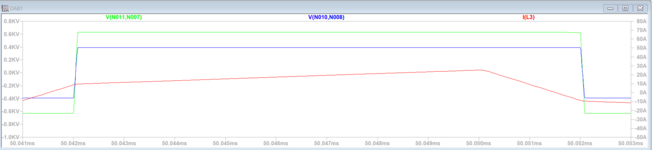

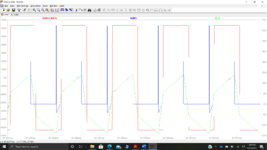

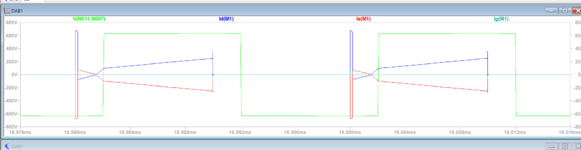

hello, I am trying to simulate Dual Active Bridge converter in LT spice. I have try simulation in Matlab Simulink where I am getting the desired phase shift. But i am simulating in LT spice, I am not able to produce the phase shift b/w the primary and secondary of the coupled inductor transformer.

As the power and voltage level linking the primary and the secondary of the transformer are different, I should choose different Mosfet switches for the each bridge and does these Mosfet have Parasitic capacitance parallel from drain to source. Or else I should place a capacitor in parallel to have the operation of soft switching. Any suggestion how to obtain the phase shift and Zero voltage switching.

As the power and voltage level linking the primary and the secondary of the transformer are different, I should choose different Mosfet switches for the each bridge and does these Mosfet have Parasitic capacitance parallel from drain to source. Or else I should place a capacitor in parallel to have the operation of soft switching. Any suggestion how to obtain the phase shift and Zero voltage switching.