genxium

Junior Member level 3

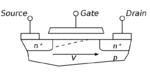

I'm learning CMOS course currently, when I review the "pinch-off" today I found that I didn't understand the "direction of pinch" in NMOS, so I went to wikipedia for help: MOSFET - Wikipedia, the free encyclopedia , it's so weird that this graph showed up in the saturation mode part, why the voltage direction is from Source to Drain?

Isn't that in saturation, the Drain voltage should be larger than both Gate and Source (as wikipedia itself stated)? Confused......

Isn't that in saturation, the Drain voltage should be larger than both Gate and Source (as wikipedia itself stated)? Confused......