viperpaki007

Full Member level 5

Hi,

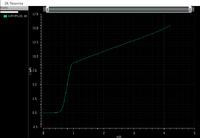

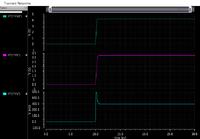

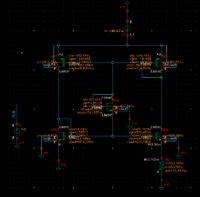

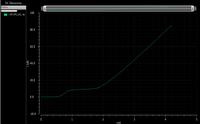

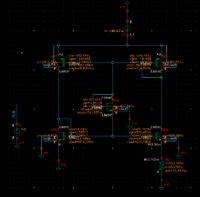

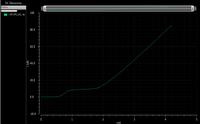

I am making a supply independent bias circuit as shown in Razavi CMOS integrated circuit book (Figure 11.5). I simulated the circuit but it does not seem to work properly. See output current vs vdd supply curve attached with this email. Can some body help? Circuit has following W and L values:

MN0 W= 28u L=1.4u

MN2 W= 7u L=1.4u

MN3 W= 7u L=1.4u

MP1 W= 14u L=1.4u

MP2 W= 14u L=1.4u

Moreover, i really can't understand how the start up circuit consisting of MN3 works. Can somebody explain this as well.

regards

I am making a supply independent bias circuit as shown in Razavi CMOS integrated circuit book (Figure 11.5). I simulated the circuit but it does not seem to work properly. See output current vs vdd supply curve attached with this email. Can some body help? Circuit has following W and L values:

MN0 W= 28u L=1.4u

MN2 W= 7u L=1.4u

MN3 W= 7u L=1.4u

MP1 W= 14u L=1.4u

MP2 W= 14u L=1.4u

Moreover, i really can't understand how the start up circuit consisting of MN3 works. Can somebody explain this as well.

regards