hkBattousai

Advanced Member level 4

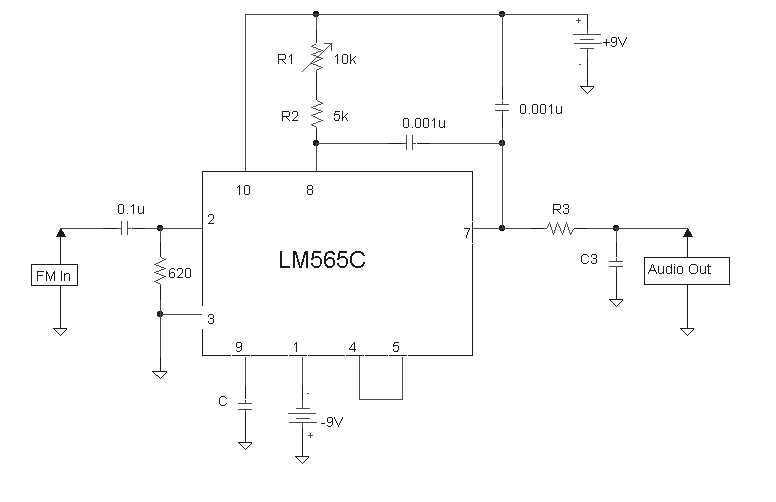

lm565

**broken link removed**

I want to design a transmitter/receiver pair communicating via FSK modulation. I decided to design the transmitter side by a VCO. And I plan using LM565 on the receiver side.

At this point I need an explanation about the operation of the LM565 IC.

From my understanding (after half-an-hour search in datasheets and sample circuits on the web), this IC has two inputs; pins 2 and 3. The internal 'phase comparetor' consists of a product modulator and a low pass filter. The output of this LPF gives a voltage level which is proportional to the difference between the frequencies of these two input signals. We can probe this voltage level from the 7th pin of LM565.

I have two questions to ask :

Q1) Is my explanation above correct? Does LM565 really work as I explained, or operate in a different manner? Is there anything necessary to correct or add?

Q2) Can you explain me the function of the internal VCO of LM565? Can I leave the 4th, 8th and 9th pins not connected?

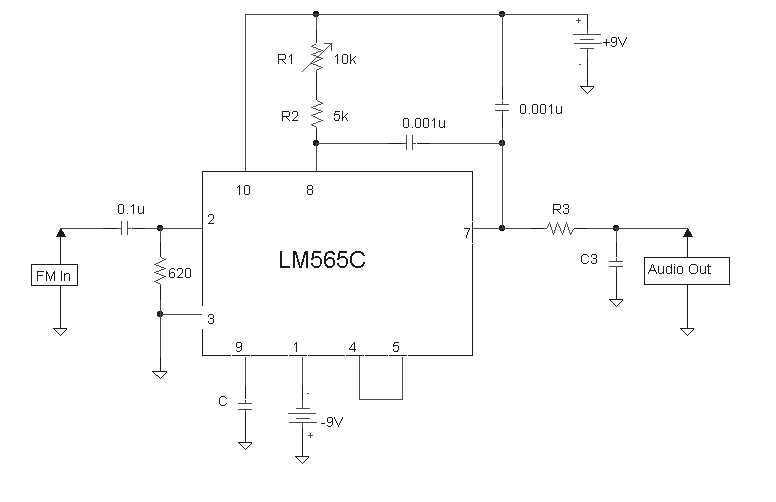

**broken link removed**

I want to design a transmitter/receiver pair communicating via FSK modulation. I decided to design the transmitter side by a VCO. And I plan using LM565 on the receiver side.

At this point I need an explanation about the operation of the LM565 IC.

From my understanding (after half-an-hour search in datasheets and sample circuits on the web), this IC has two inputs; pins 2 and 3. The internal 'phase comparetor' consists of a product modulator and a low pass filter. The output of this LPF gives a voltage level which is proportional to the difference between the frequencies of these two input signals. We can probe this voltage level from the 7th pin of LM565.

I have two questions to ask :

Q1) Is my explanation above correct? Does LM565 really work as I explained, or operate in a different manner? Is there anything necessary to correct or add?

Q2) Can you explain me the function of the internal VCO of LM565? Can I leave the 4th, 8th and 9th pins not connected?