Bryan79

Newbie level 5

causes fordead zone in pll

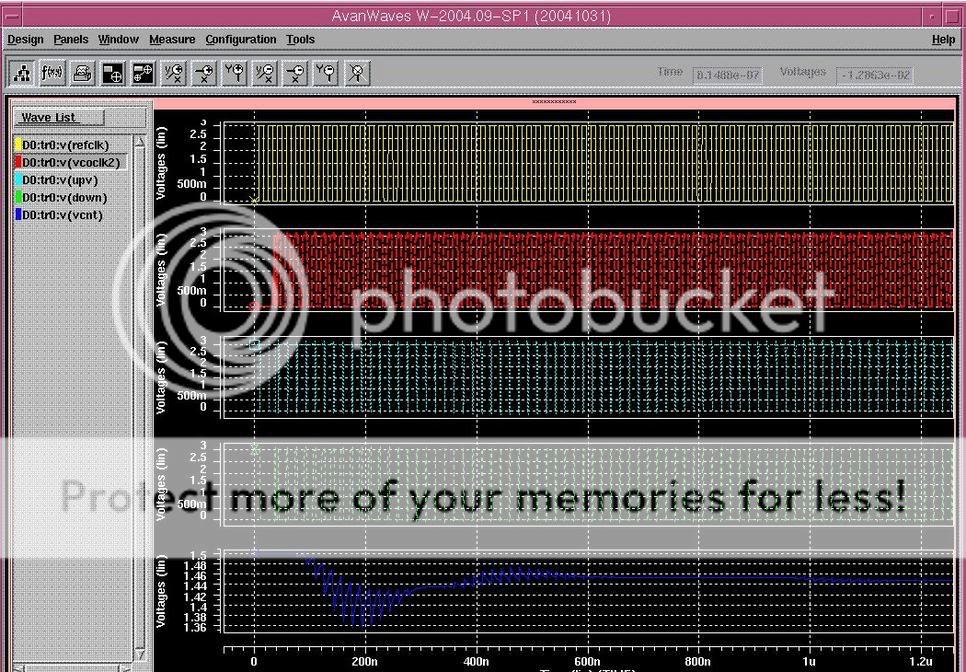

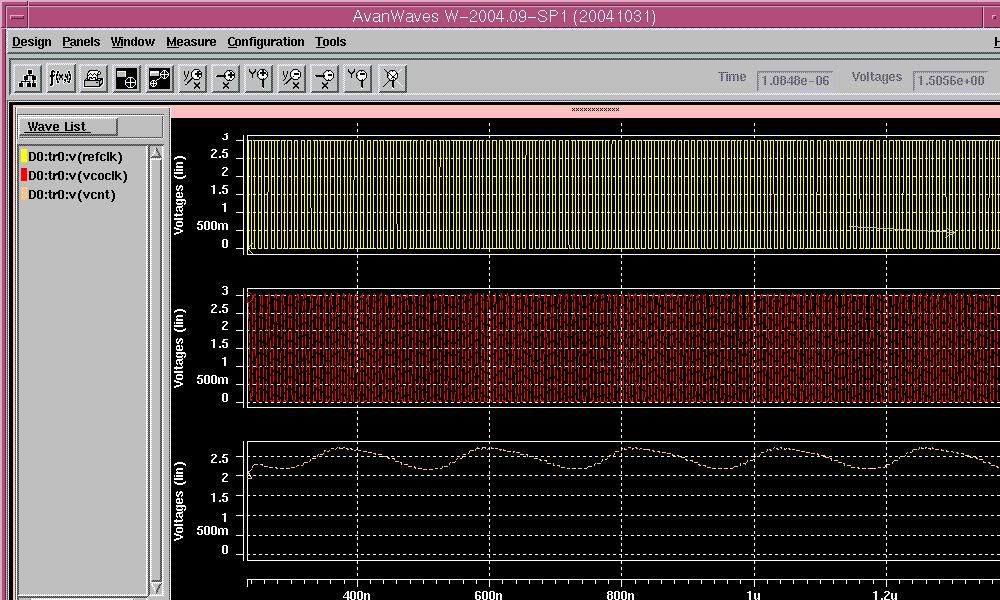

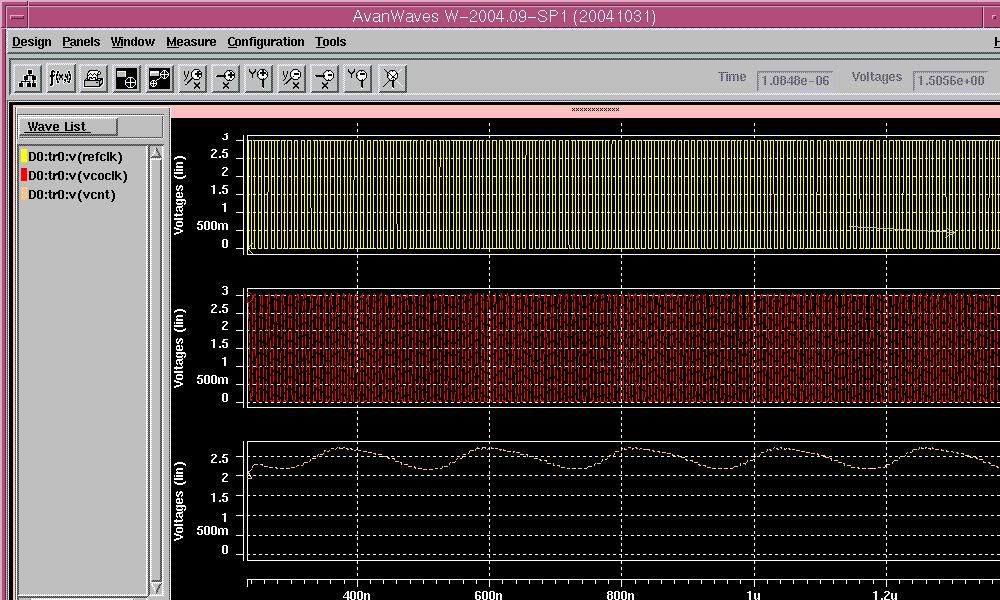

Hi, I have designed a simple PLL circuit using PFD, 3rd order type type 2 filter, a charge pump and a ring oscillator type VCO.

I notice the control voltage (vcnt) of VCO oscillates and cannot settle down.

Anyone know any idea what is wrong? I have tried to make my charge pump current matches, eliminate dead-zone in PFD by adding delay to reset path and adjusting the R,C of the filter. But it still gives me oscillating control voltage.

Thanks.

Hi, I have designed a simple PLL circuit using PFD, 3rd order type type 2 filter, a charge pump and a ring oscillator type VCO.

I notice the control voltage (vcnt) of VCO oscillates and cannot settle down.

Anyone know any idea what is wrong? I have tried to make my charge pump current matches, eliminate dead-zone in PFD by adding delay to reset path and adjusting the R,C of the filter. But it still gives me oscillating control voltage.

Thanks.