yanzixuan

Member level 3

Hi All, I designed a counter ,and set clock constraint as follow:

create_clock -period 8 -waveform {0 4} [get_ports clk]

do compile and get the synthesised file for simulation.

the timing report as follow([all_registers])

Point Incr Path

--------------------------------------------------------------------------

clock clk (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

main_cnt_reg[0]/CK (DFFRHQX1) 0.00 0.00 r

main_cnt_reg[0]/Q (DFFRHQX1) 0.27 0.27 r

add_18/A[0] (main_cnt_DW01_inc_1) 0.00 0.27 r

add_18/U1_1_1/CO (ADDHXL) 0.13 0.40 r

add_18/U1_1_2/CO (ADDHXL) 0.12 0.52 r

add_18/U1_1_3/CO (ADDHXL) 0.12 0.65 r

add_18/U1_1_4/CO (ADDHXL) 0.12 0.77 r

add_18/U1_1_5/CO (ADDHXL) 0.12 0.90 r

add_18/U1_1_6/CO (ADDHXL) 0.12 1.02 r

add_18/U1_1_7/CO (ADDHXL) 0.12 1.15 r

add_18/U1_1_8/CO (ADDHXL) 0.12 1.27 r

add_18/U1_1_9/CO (ADDHXL) 0.12 1.39 r

add_18/U2/Y (XOR2X1) 0.12 1.51 f

add_18/SUM[10] (main_cnt_DW01_inc_1) 0.00 1.51 f

main_cnt_reg[10]/D (DFFRHQX1) 0.00 1.51 f

data arrival time 1.51

clock clk (rise edge) 8.00 8.00

clock network delay (ideal) 0.00 8.00

main_cnt_reg[10]/CK (DFFRHQX1) 0.00 8.00 r

library setup time -0.21 7.79

data required time 7.79

--------------------------------------------------------------------------

data required time 7.79

data arrival time -1.51

--------------------------------------------------------------------------

slack (MET) 6.27

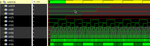

but when I do the simulation, the wave is no correct:

if I slowdown the frequency, the waveform is right.

so it's strange for me. if the design pass the timing constraint, how could this error be possible.

Any one can help? BOW~~

create_clock -period 8 -waveform {0 4} [get_ports clk]

do compile and get the synthesised file for simulation.

the timing report as follow([all_registers])

Point Incr Path

--------------------------------------------------------------------------

clock clk (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

main_cnt_reg[0]/CK (DFFRHQX1) 0.00 0.00 r

main_cnt_reg[0]/Q (DFFRHQX1) 0.27 0.27 r

add_18/A[0] (main_cnt_DW01_inc_1) 0.00 0.27 r

add_18/U1_1_1/CO (ADDHXL) 0.13 0.40 r

add_18/U1_1_2/CO (ADDHXL) 0.12 0.52 r

add_18/U1_1_3/CO (ADDHXL) 0.12 0.65 r

add_18/U1_1_4/CO (ADDHXL) 0.12 0.77 r

add_18/U1_1_5/CO (ADDHXL) 0.12 0.90 r

add_18/U1_1_6/CO (ADDHXL) 0.12 1.02 r

add_18/U1_1_7/CO (ADDHXL) 0.12 1.15 r

add_18/U1_1_8/CO (ADDHXL) 0.12 1.27 r

add_18/U1_1_9/CO (ADDHXL) 0.12 1.39 r

add_18/U2/Y (XOR2X1) 0.12 1.51 f

add_18/SUM[10] (main_cnt_DW01_inc_1) 0.00 1.51 f

main_cnt_reg[10]/D (DFFRHQX1) 0.00 1.51 f

data arrival time 1.51

clock clk (rise edge) 8.00 8.00

clock network delay (ideal) 0.00 8.00

main_cnt_reg[10]/CK (DFFRHQX1) 0.00 8.00 r

library setup time -0.21 7.79

data required time 7.79

--------------------------------------------------------------------------

data required time 7.79

data arrival time -1.51

--------------------------------------------------------------------------

slack (MET) 6.27

but when I do the simulation, the wave is no correct:

if I slowdown the frequency, the waveform is right.

so it's strange for me. if the design pass the timing constraint, how could this error be possible.

Any one can help? BOW~~