Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

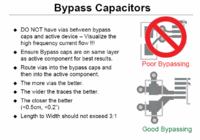

It depends on the frequencies involved. My preference is not to have vias between the decoupling capacitor and the IC - they add inductance; not much, but at 500MHz or more you will notice it. So, I would put the vias to the left of the decoupling capacitor and directly decouple the IC with the PCB tracks. Some IC pinouts make that impractical so you have to use vias somewhere between the decoupler and the device.

Keith.

A is the correct way it gives the lowest possible inductance, which is the controlling factor in cap placement and achieving the best decoupling.

Marc,

Many thanks for that - I will print those off for reading at leisure. At first glance they look interesting because they cover some of the real world problems of pins not being where you would want them so you have to use vias. Interesting about mounting capacitors on their sides. For some recent work I was trying to find capacitors which didn't have the "wrap around" ends as they increase inductance.

Keith

the side mounting only helps with moving the PRF's much higher (i think). Your SRF still needs a lower inductance design to be improved.