neoflash

Advanced Member level 1

Hi guys,

Just come up with a strange issue with MDAC design in pipelined ADC.

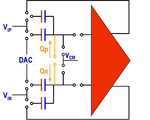

It is a flip-around 1.5bit/stage MDAC with op-amp sharing. I applied DC input so that memory is not an issue.

The gain loss I observed is that gain is 1.984 instead of 2.0. With op-amp gain at ~500, I should be able to get ~1.996 MDAC gain.

After painful debugging, I found that it is from the equalizing switch (yellow switch in diagram), it is dumping non-equal charge into differential capacitors. If I remove this switch, the gain of MDAC goes back to 1.996 as predicted by calculation.

I plotted the drain/source current. The integral indeed is different out of drain side and source side.

I tried to split this switch into 2 transistors and make sure source/drain confusion will not happen. However, it doesn't change the result at all.

It seems like this NMOS does like to discharge its channel Q unevenly in this case. However, other switches in this scheme doesn't have this issue.

I'm stuck at here. Not sure what is going wrong here.

BTW, this gain loss is quite consistent at different input amplitude. It change very little from 1x input to 5x input. The gain is always 1.984xxx.

Please suggest your kind inputs. Thanks.

Neo

Just come up with a strange issue with MDAC design in pipelined ADC.

It is a flip-around 1.5bit/stage MDAC with op-amp sharing. I applied DC input so that memory is not an issue.

The gain loss I observed is that gain is 1.984 instead of 2.0. With op-amp gain at ~500, I should be able to get ~1.996 MDAC gain.

After painful debugging, I found that it is from the equalizing switch (yellow switch in diagram), it is dumping non-equal charge into differential capacitors. If I remove this switch, the gain of MDAC goes back to 1.996 as predicted by calculation.

I plotted the drain/source current. The integral indeed is different out of drain side and source side.

I tried to split this switch into 2 transistors and make sure source/drain confusion will not happen. However, it doesn't change the result at all.

It seems like this NMOS does like to discharge its channel Q unevenly in this case. However, other switches in this scheme doesn't have this issue.

I'm stuck at here. Not sure what is going wrong here.

BTW, this gain loss is quite consistent at different input amplitude. It change very little from 1x input to 5x input. The gain is always 1.984xxx.

Please suggest your kind inputs. Thanks.

Neo