electrophile

Member level 2

- Joined

- Aug 30, 2013

- Messages

- 48

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Activity points

- 1,677

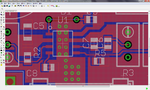

I'm a new Eagle user and I created an SOIC part with a small heat pad in the middle. The pad is on the bottom and at the top copper layers. The bottom pad is purely for soldering convenience sake. Its easy to solder the pad by heating the bottom pad with your soldering iron. Now, the board has 2 layers and the bottom one is all GND. I've attached an image here. The manufacturer says that I should extend the heat pad beyond the IC and put some vias so that heat is transferred to a larger plane. Now I've put these vias and named them GND but I keep getting an "Overlap" error. Why is this? Also all the copper pours are created with zero widths because it gave me better control over the fill and now I get "Width errors". How do I resolve these?