Farad22

Junior Member level 2

Hi,

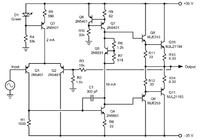

I have a question about the voltage amplification stage of an (audio) amplifier. I just took this attached schematic as an example. The VAS transistor Q4 is driven by the output current from the input pair. It is said the VAS (Voltage Amplification Stage) is a transimpedance stage, converting a current input into a voltage output. But where does this output voltage originates? For example, in the case of a simple common emitter amplifier with a load resistor in the collector path the collector current is converted to a voltage by this load resistor. That's easy to see. But how does this work in the attached schematic, where the load is a current source combined with the output load buffered by the emitter followers.

Where in this schematic is the voltage "created" to provide the output voltage swing to drive the load? Thanks !

I have a question about the voltage amplification stage of an (audio) amplifier. I just took this attached schematic as an example. The VAS transistor Q4 is driven by the output current from the input pair. It is said the VAS (Voltage Amplification Stage) is a transimpedance stage, converting a current input into a voltage output. But where does this output voltage originates? For example, in the case of a simple common emitter amplifier with a load resistor in the collector path the collector current is converted to a voltage by this load resistor. That's easy to see. But how does this work in the attached schematic, where the load is a current source combined with the output load buffered by the emitter followers.

Where in this schematic is the voltage "created" to provide the output voltage swing to drive the load? Thanks !