cupoftea

Advanced Member level 5

Hi,

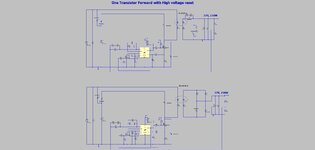

The following are both one tran forwards (LTspice and jpeg) .....with well known output rectifiers.

1.....Well known Direct diode rectifier

2...Well known Capacitively coupled rectifier

Do you agree that the capacively coupled output rectifier is a waste of time?......the peak currents are way higher...OK, the voltage on the output diode is much less...but so what...you can get 900V fast diodes....and 900V sync FETs.

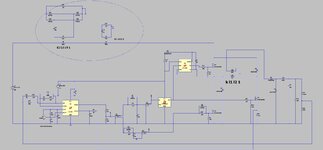

The following are both one tran forwards (LTspice and jpeg) .....with well known output rectifiers.

1.....Well known Direct diode rectifier

2...Well known Capacitively coupled rectifier

Do you agree that the capacively coupled output rectifier is a waste of time?......the peak currents are way higher...OK, the voltage on the output diode is much less...but so what...you can get 900V fast diodes....and 900V sync FETs.