mohamis288

Full Member level 3

Hello,

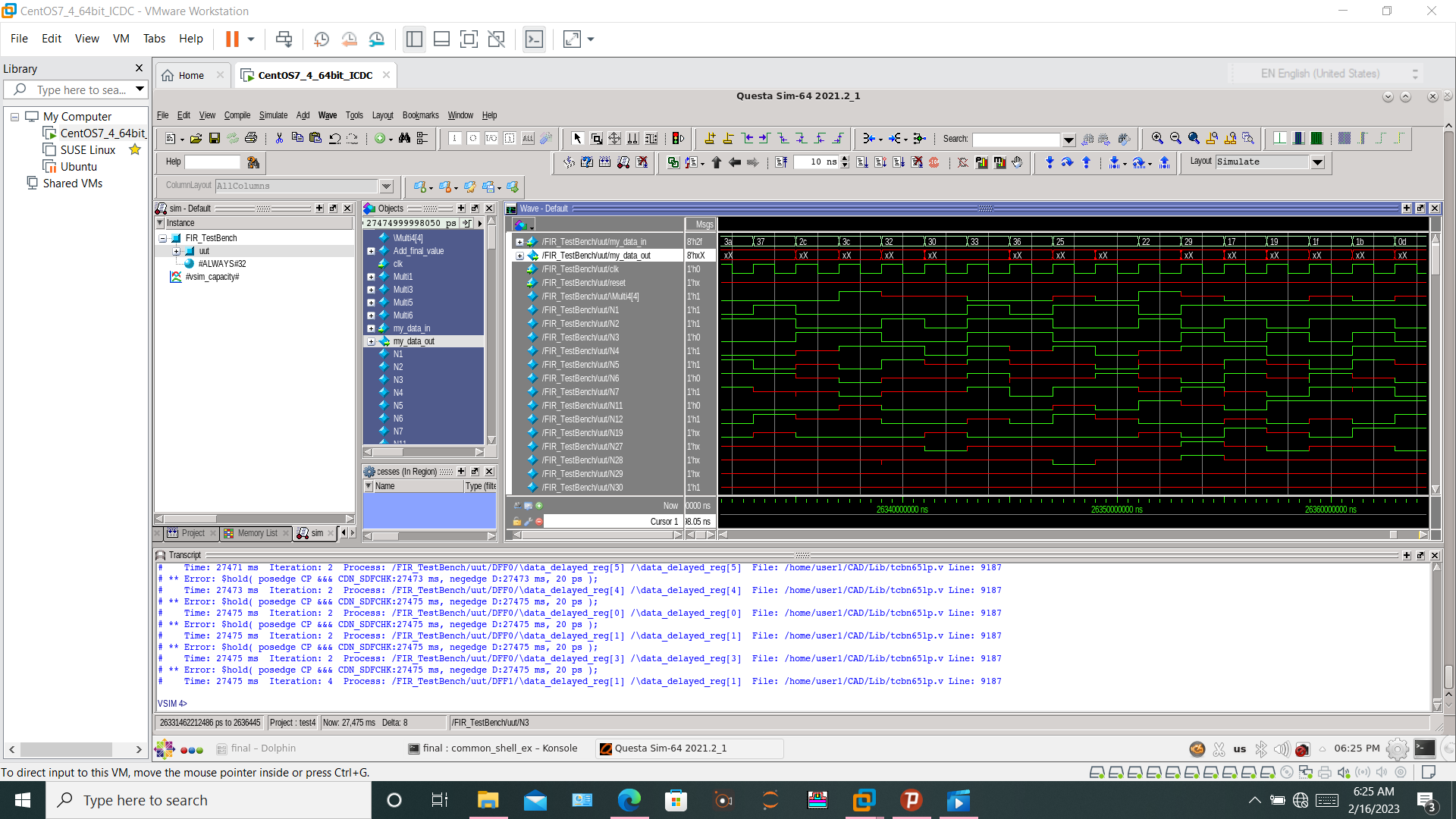

I have simulated the 8-bit FIR filter in Questa, But as you can see some ports are in 'don't care' status. I am new to the digital design. so I need your help.

I have used design vision to synthesize my Verilog code. But I did not define the clock period, input delay, output delay and ...

is this problem related to that? how can I solve it?

BR

I have simulated the 8-bit FIR filter in Questa, But as you can see some ports are in 'don't care' status. I am new to the digital design. so I need your help.

I have used design vision to synthesize my Verilog code. But I did not define the clock period, input delay, output delay and ...

is this problem related to that? how can I solve it?

BR