dipanjan

Member level 2

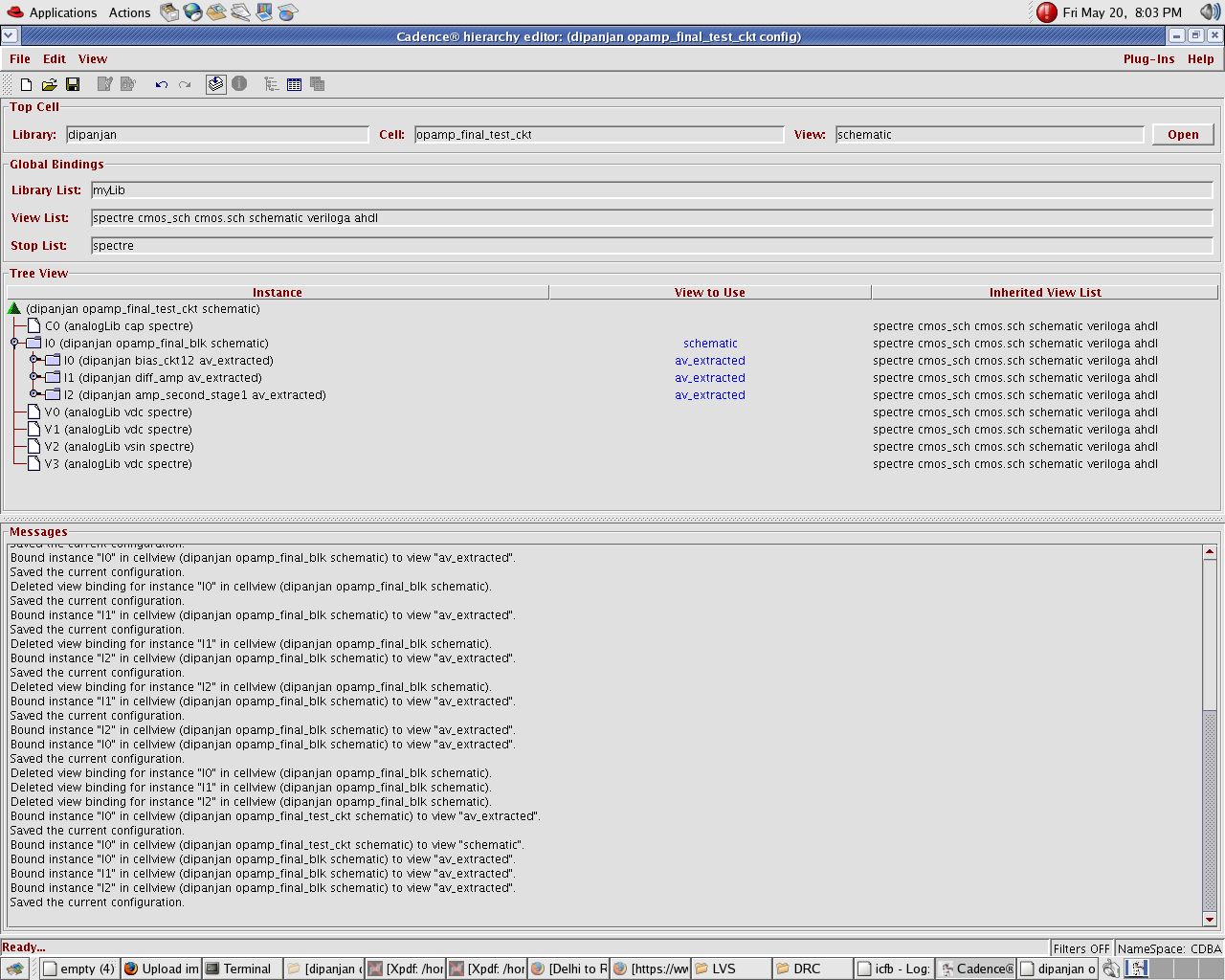

opamp post layout simulation... urgent very very urgent

hi i designed an opamp schematic....

on simulation the schematic is giving a gain of around 30dB

but after layout the post simulation result is bizarre....it is giving nearly 90dB....i was expecting tsome change in gain but how come the performances changed completely???.

how come it is increasing that too so much

any idea wat is happening??

hi i designed an opamp schematic....

on simulation the schematic is giving a gain of around 30dB

but after layout the post simulation result is bizarre....it is giving nearly 90dB....i was expecting tsome change in gain but how come the performances changed completely???.

how come it is increasing that too so much

any idea wat is happening??