cupoftea

Advanced Member level 5

Hi,

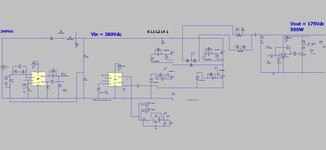

Attached (LTspice and PDF schem) is a 500W offline Full Bridge SMPS in on/off control. Its duty cycle is clamped at just above the max that it would need to be if this was a “normal” full bridge.

Current limit is at the peak needed for max power.

There is no slope compensation as its not needed, even though duty cycle is 0.68.

Would you say there is any reason that this SMPS should fail EMC, compared to a “normal” frequency compensated Full Bridge?

Attached (LTspice and PDF schem) is a 500W offline Full Bridge SMPS in on/off control. Its duty cycle is clamped at just above the max that it would need to be if this was a “normal” full bridge.

Current limit is at the peak needed for max power.

There is no slope compensation as its not needed, even though duty cycle is 0.68.

Would you say there is any reason that this SMPS should fail EMC, compared to a “normal” frequency compensated Full Bridge?