analog_curious

Member level 2

All,

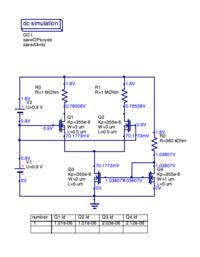

I have a differential amplifier with resistive load. I biased the diff. amp by a tail current source which carries 2*Id (Id is for each side of the input NMOS transistor). Then I tried replacing this tail current source by a NMOS current mirror which gives the same output current as my required current realized through current source.

The issue I am facing is that I am not able to get the same current through my current mirror configuration when I connect it to the source end of my input NMOS circuit. I realize the reason because the Vds is not the same anymore in my current mirror and so I dont see the current I want

I see many circuits online implemented with NMOS current mirrors for NMOS input transistors of differential stage in which they use a separate DC bias at the gate to realise the same Vds condition for current mirror. But then the biasing is dependent on threshold voltage of input transistors.It shouldnt be the case for current mirrors usually right?

Did I understand wrong or..?

Guidances and suggestions are welcome

Dan

I have a differential amplifier with resistive load. I biased the diff. amp by a tail current source which carries 2*Id (Id is for each side of the input NMOS transistor). Then I tried replacing this tail current source by a NMOS current mirror which gives the same output current as my required current realized through current source.

The issue I am facing is that I am not able to get the same current through my current mirror configuration when I connect it to the source end of my input NMOS circuit. I realize the reason because the Vds is not the same anymore in my current mirror and so I dont see the current I want

I see many circuits online implemented with NMOS current mirrors for NMOS input transistors of differential stage in which they use a separate DC bias at the gate to realise the same Vds condition for current mirror. But then the biasing is dependent on threshold voltage of input transistors.It shouldnt be the case for current mirrors usually right?

Did I understand wrong or..?

Guidances and suggestions are welcome

Dan