wandola

Junior Member level 3

I am a newbie. I designed a PCB without any supervision 'cause I have nobody to consult.

It is a 4-layer PCB to test a ADC chip. The PCB is shown below.

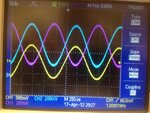

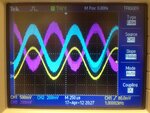

I found that my differential AC signals to the ADC input have been distorted. I think the clk signal is coupled to the the ground plane first. Then coupled to other part of the circuit.

Indeed, the power supply, the LDO output, and even ground plane are all distorted by a periodic signal which is in accordance with the clk.

Is there anything I can do to solve this problem? Or I have to redesign a new PCB...

Pls help the newbie...

It is a 4-layer PCB to test a ADC chip. The PCB is shown below.

I found that my differential AC signals to the ADC input have been distorted. I think the clk signal is coupled to the the ground plane first. Then coupled to other part of the circuit.

Indeed, the power supply, the LDO output, and even ground plane are all distorted by a periodic signal which is in accordance with the clk.

Is there anything I can do to solve this problem? Or I have to redesign a new PCB...

Pls help the newbie...