xVoid

Newbie level 1

g1,g2 ....... onn ...... +ve voltage

g2,g3 .......onn........ 0 zero voltage

g3,g4 ........onn ....... -ve voltage

it is the switching theme..!

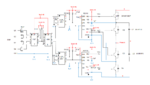

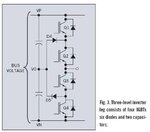

hi i have attached the above diagrams of NPC inverter topology the basic question is about the attachment of the driver ic ir2110 i think two ir2110 ic are required the two above mosfets should have the HIN of the ir 2110 ic and the lower mosfets should have LIN from respective driver ic ... then the basic issue which arises there is that can the driver circuit independently help in driving the two high side mosfets .. with the HIN1 and HIN2 (as there are two driver ic).

and the ground of the circuit should be the ground of the npc or there needs to be some other implementation making the ground of one driver the npc ground and connecting the other ir 2110 ground to the negative side of npc... was just assuming ..!

even tough i will upload one proteus file showing the circuit will u please help in its driver connection..! :-D