BKI

Member level 1

- Joined

- Jul 23, 2014

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Activity points

- 264

Hi,

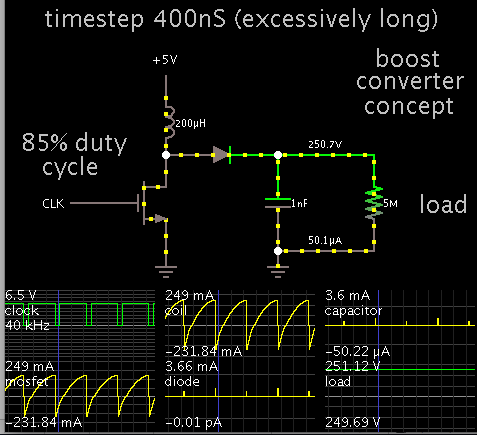

i have designed a Boost Converter that generates 250V from 5V supply. It operates in DCM, has a high impedance output (5Mohm) and low output current (50uA).

The MOSFET has a input signal with a frequency of 40kHz and Duty Cycle of 0.9. In the Cadence simulation, the circuit works well, but the inductor current looks strange.

When the MOSFET is switched off, the inductor current falls in negative current range. So, the inductor peak current is around 740mA and the minimum inductor current is around -40mA. I am using a external real diode model from Vishay (byg20j) for Cadence simulation.

What can be the reason for the negative inductor current?

I am not sure if i have to worry about it!

Thanks in advance for your help!

i have designed a Boost Converter that generates 250V from 5V supply. It operates in DCM, has a high impedance output (5Mohm) and low output current (50uA).

The MOSFET has a input signal with a frequency of 40kHz and Duty Cycle of 0.9. In the Cadence simulation, the circuit works well, but the inductor current looks strange.

When the MOSFET is switched off, the inductor current falls in negative current range. So, the inductor peak current is around 740mA and the minimum inductor current is around -40mA. I am using a external real diode model from Vishay (byg20j) for Cadence simulation.

What can be the reason for the negative inductor current?

I am not sure if i have to worry about it!

Thanks in advance for your help!