wandola

Junior Member level 3

Hey guys,

I have a three-stage LDO.

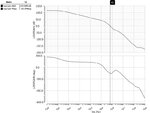

The simulation result is in attached (without compensation).

Looks like the dominant pole is only about 19 Hz, the second pole is around 90 kHz. UGB freq = 640 kHz.

The dominant pole is too low. And the DC gain is too high.

I tried to do a miller compensation. It turns out the dominant pole moves to very very low frequency (<1 Hz). And the compensation cap needs to be huge ~100 pF.

I am wondering is there other ways to do the compensation. I am not an expert in LDO/Opamp design. My specialization is in SAR ADC design.

thanks a lot guys.

I have a three-stage LDO.

The simulation result is in attached (without compensation).

Looks like the dominant pole is only about 19 Hz, the second pole is around 90 kHz. UGB freq = 640 kHz.

The dominant pole is too low. And the DC gain is too high.

I tried to do a miller compensation. It turns out the dominant pole moves to very very low frequency (<1 Hz). And the compensation cap needs to be huge ~100 pF.

I am wondering is there other ways to do the compensation. I am not an expert in LDO/Opamp design. My specialization is in SAR ADC design.

thanks a lot guys.