MrUmunhum

Newbie level 4

Hi group,

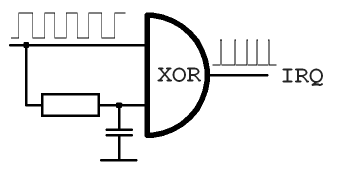

I need to create an interrupt on a state change of a GPIO pin. I'm thinking something like the attached circuit but I don't know which IC to use. I don't want to use a Micro CPU. The circuit will use an XOR IC to detect a change of state, then trigger the Sync pulse and store the new state.

I need to monitor 8 GPIO pins.

Any ideas?

Thanks for your time.

---------- Post added at 21:25 ---------- Previous post was at 20:40 ----------

Will this work?

I need to create an interrupt on a state change of a GPIO pin. I'm thinking something like the attached circuit but I don't know which IC to use. I don't want to use a Micro CPU. The circuit will use an XOR IC to detect a change of state, then trigger the Sync pulse and store the new state.

I need to monitor 8 GPIO pins.

Any ideas?

Thanks for your time.

---------- Post added at 21:25 ---------- Previous post was at 20:40 ----------

Will this work?