want_to_see

Newbie level 6

hello all,

Im having problem with a half bridge.

The sides seem to be fighting which is generating heat.

The isolated section of circuit causing the problems is a mosfet driver (IDD614) and matched N and P mosfet array (FMP26)

It is being driven from a function generator with 5V peak to peak square wave centered at 2.5V.

The circuit has been built many times over and I keep having the same problems.

Ive even gone as far as to make a PCB which has teh same problems.

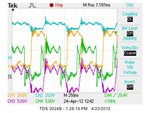

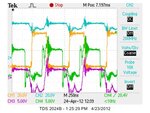

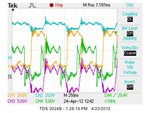

Throughtout the next few images, the same color convention is used where:

yellow: output (pin3 fmp26), blue: p channel gate ( fmp pin 5), pink: n channel gate (fmp pin 1), green: fnction generator input (idd pin 4).

This is the waveform when the circuit is switching 12V

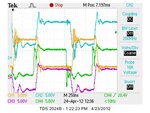

Switching 60V

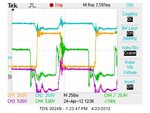

this is the output with just the function generator on and power supply swtiched off

is it a loading issue? I just dont understand this.

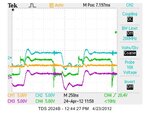

As the rate of switching speed is increated, the "fighting" takes up a larger percentage of the waveform.

When a the load (1nf capacitor) is connected at teh frequency i want to run at, 1.2Mhz,, the loading becomes worse

When I was searching for a solution to this, I came upon this post when i why i registered.

Its somewhat similar but the load here is capacative not inductive.

I realy appreciate any help i can get on this.

https://www.edaboard.com/threads/241410/

Im having problem with a half bridge.

The sides seem to be fighting which is generating heat.

The isolated section of circuit causing the problems is a mosfet driver (IDD614) and matched N and P mosfet array (FMP26)

It is being driven from a function generator with 5V peak to peak square wave centered at 2.5V.

The circuit has been built many times over and I keep having the same problems.

Ive even gone as far as to make a PCB which has teh same problems.

Throughtout the next few images, the same color convention is used where:

yellow: output (pin3 fmp26), blue: p channel gate ( fmp pin 5), pink: n channel gate (fmp pin 1), green: fnction generator input (idd pin 4).

This is the waveform when the circuit is switching 12V

Switching 60V

this is the output with just the function generator on and power supply swtiched off

is it a loading issue? I just dont understand this.

As the rate of switching speed is increated, the "fighting" takes up a larger percentage of the waveform.

When a the load (1nf capacitor) is connected at teh frequency i want to run at, 1.2Mhz,, the loading becomes worse

When I was searching for a solution to this, I came upon this post when i why i registered.

Its somewhat similar but the load here is capacative not inductive.

I realy appreciate any help i can get on this.

https://www.edaboard.com/threads/241410/