psychoticjoe

Newbie level 3

Hello,

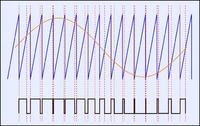

I am a newbie to verilog and just got a hold of a FPGA Spartan 3E board but now im in need of some help. Of course I have done a lot of searching and reading first. Anyways, the task I am faced with is to use a Look-up table to generate PWM that will be outputted into an RC filter which will convert my PWM to a 60 Hz sinewave. My board runs at 50 MHz. I am not sure how to use the look up table to create the PWM that will eventually become a 60 Hz sine wave.

ANY feedback is greatly appreciated!

Thanks,

Joe

I am a newbie to verilog and just got a hold of a FPGA Spartan 3E board but now im in need of some help. Of course I have done a lot of searching and reading first. Anyways, the task I am faced with is to use a Look-up table to generate PWM that will be outputted into an RC filter which will convert my PWM to a 60 Hz sinewave. My board runs at 50 MHz. I am not sure how to use the look up table to create the PWM that will eventually become a 60 Hz sine wave.

ANY feedback is greatly appreciated!

Thanks,

Joe