Junus2012

Advanced Member level 5

Hello,

is it possible to linearize the MOS resistor by using a poly resistor in parallel to it ?

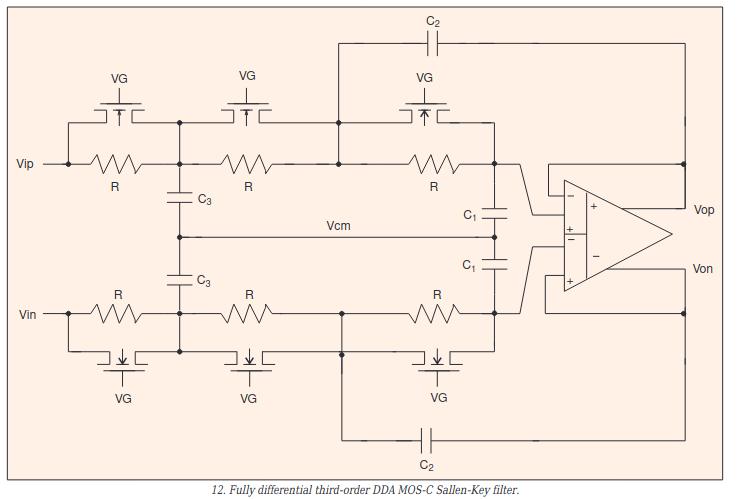

please refer to the below picture, the author is running the filter by varying the gate of the transistor while he kept a resistor in parallel,

In my opinion, if i want to cancel the non linearity if the NMOS then I must connect a device with opposite charasteritcis, while the poly resistor is linear, I am not sure how it is working

thanks

is it possible to linearize the MOS resistor by using a poly resistor in parallel to it ?

please refer to the below picture, the author is running the filter by varying the gate of the transistor while he kept a resistor in parallel,

In my opinion, if i want to cancel the non linearity if the NMOS then I must connect a device with opposite charasteritcis, while the poly resistor is linear, I am not sure how it is working

thanks