Siong Hui

Newbie level 6

Hi,

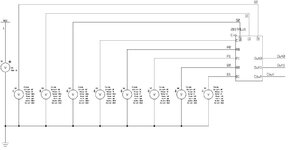

I doing a project about designing 8-bit ALU CMOS using Mentor Graphics. So, I using a hierarchical method of 2-bit ALU to form the 8-bit ALU. The simulation of 2-bit ALU is successfully, but why my simulation of 8-bit ALU is failed. For the 8-bit ALU CMOS, I need to spend one to two hours to simulate it, but the outcome is simulation failed. Does anyone have ideas on how to solve it?

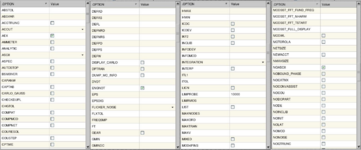

The transcript of the simulation is attached below.

I doing a project about designing 8-bit ALU CMOS using Mentor Graphics. So, I using a hierarchical method of 2-bit ALU to form the 8-bit ALU. The simulation of 2-bit ALU is successfully, but why my simulation of 8-bit ALU is failed. For the 8-bit ALU CMOS, I need to spend one to two hours to simulate it, but the outcome is simulation failed. Does anyone have ideas on how to solve it?

The transcript of the simulation is attached below.