kumar_eee

Advanced Member level 3

- Joined

- Sep 22, 2004

- Messages

- 814

- Helped

- 139

- Reputation

- 276

- Reaction score

- 113

- Trophy points

- 1,323

- Location

- Bangalore,India

- Activity points

- 4,677

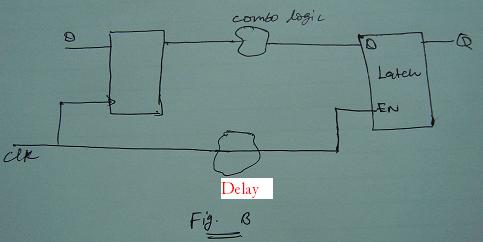

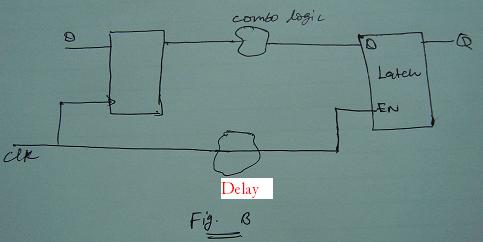

What will be the Maximum clock frequency of the circuit?

I'm confused on which edge we will calculate the setup & hold for the latch. I guess it should be the trailing one. Any suggestions?

I'm confused on which edge we will calculate the setup & hold for the latch. I guess it should be the trailing one. Any suggestions?