exhalt

Junior Member level 2

- Joined

- Jan 15, 2015

- Messages

- 21

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 131

I need a little help in this and I have been doing research for quite some time in the internet and I can't seem to find anything about how to do it. Is there any way somebody can help me in it.

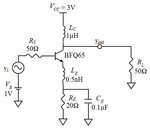

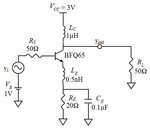

The amplifier below is operating at 1GHz ( fs = 1GHz).

As indicated in the circuit below, design a matching network (MN) circuit using a Smith Chart to match the source to the input impedance of the amplifier (ZL) for maximum power delivery.

Note you will need to consider the high frequency model for the transistor.

The amplifier below is operating at 1GHz ( fs = 1GHz).

As indicated in the circuit below, design a matching network (MN) circuit using a Smith Chart to match the source to the input impedance of the amplifier (ZL) for maximum power delivery.

Note you will need to consider the high frequency model for the transistor.

Last edited: