Fávero Santos

Junior Member level 1

Hello, all!

I was helping a student in our lab with a LVS mismatch error while using ncap cell. I verified the log of the LVS (I am using PVS) and I observed that the pin map is being updated to a new one:

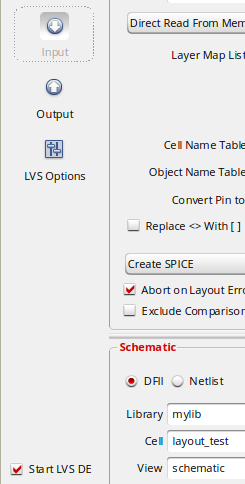

This happens when the option "DFII" is select in the "input" tab when using PVS GUI:

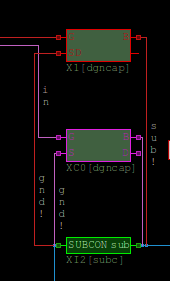

Here, I present a view of the graphical LVS debugger showing the mismatch due the pin map swap (red block: layout, pink block: schematic):

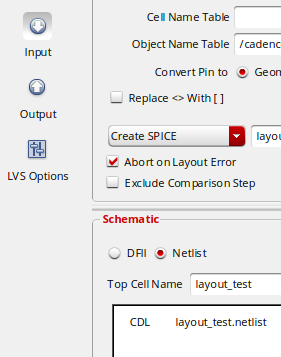

Interestingly, when I generate the CDL netlist in the schematic (via PDK->Netlisting->CDL->OK) and point the generated netlist file in the PVS GUI input tab, PVS run is clean:

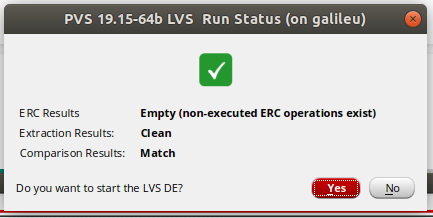

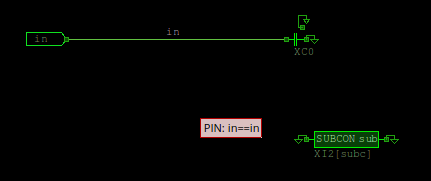

LVS debugger view:

So, finally, my question is: what is going on and how to solve this issue in such a manner there will be no need to generate the netlist file and them upload it to the PVS GUI?

Many thanks!!!

Edit: added new images for future reference.

I was helping a student in our lab with a LVS mismatch error while using ncap cell. I verified the log of the LVS (I am using PVS) and I observed that the pin map is being updated to a new one:

This happens when the option "DFII" is select in the "input" tab when using PVS GUI:

Here, I present a view of the graphical LVS debugger showing the mismatch due the pin map swap (red block: layout, pink block: schematic):

Interestingly, when I generate the CDL netlist in the schematic (via PDK->Netlisting->CDL->OK) and point the generated netlist file in the PVS GUI input tab, PVS run is clean:

LVS debugger view:

So, finally, my question is: what is going on and how to solve this issue in such a manner there will be no need to generate the netlist file and them upload it to the PVS GUI?

Many thanks!!!

Edit: added new images for future reference.