hoi

Newbie level 5

Hi everyone,

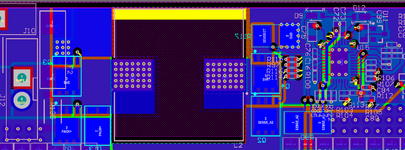

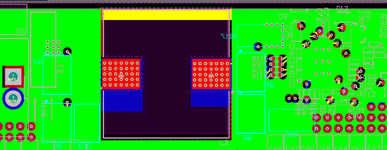

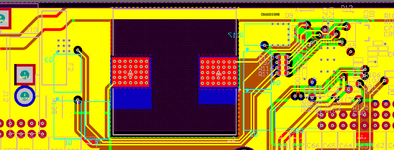

I am making a battery charger with LTC4020 to charge 12S li-lon battery but having problems for months and still could not fix it.

Input 24V

output 43V 2.5A charge current

battery voltage range 24V-43V (cell voltage 2V - 3.6V)

schematic setting

Maximum input current 10A

charging current 2.5A

battery float voltage 42.86V

Maximum output voltage 43.7V

Precharge voltage 28V

Problem

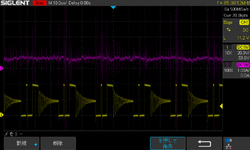

The charge current is lower than expected value, it should be maximum 2.5A but I could only get 0.5-1A charging current. And the waveform is strange.

I tried to tuned Vc and ITH value for weeks, it change a little bit with different value but could not solve the problem.

I tried to contact local FAE but did not get any useful information, tried to post the question in AnalogDevices forum but no one reply. Google searching LTC4020 and it seems some people here are using this chip so I think maybe I could get help from here. I would really appreciate if anyone could help.

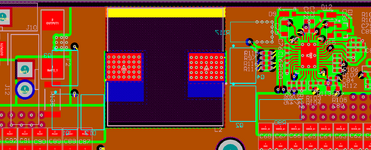

The attachment is schematic, waveform of SW2 and charge current.

Thanks

I am making a battery charger with LTC4020 to charge 12S li-lon battery but having problems for months and still could not fix it.

Input 24V

output 43V 2.5A charge current

battery voltage range 24V-43V (cell voltage 2V - 3.6V)

schematic setting

Maximum input current 10A

charging current 2.5A

battery float voltage 42.86V

Maximum output voltage 43.7V

Precharge voltage 28V

Problem

The charge current is lower than expected value, it should be maximum 2.5A but I could only get 0.5-1A charging current. And the waveform is strange.

I tried to tuned Vc and ITH value for weeks, it change a little bit with different value but could not solve the problem.

I tried to contact local FAE but did not get any useful information, tried to post the question in AnalogDevices forum but no one reply. Google searching LTC4020 and it seems some people here are using this chip so I think maybe I could get help from here. I would really appreciate if anyone could help.

The attachment is schematic, waveform of SW2 and charge current.

Thanks

Attachments

Last edited: