dyunasing

Junior Member level 3

Hi, all,

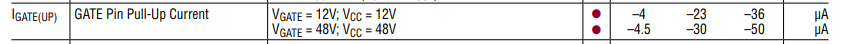

I have difficulty to understand one of the spec in LT4356 datasheet.

I had thought this gate pin pull up current is to source current to charge the mosfet parasitic capacitance and any external capacitor on the gate.

This has to be positive, right?

And this to be fairly large, right, as peak current is concerned?

Could anyone help to enlighten me? Thank you.

Dyu

I have difficulty to understand one of the spec in LT4356 datasheet.

I had thought this gate pin pull up current is to source current to charge the mosfet parasitic capacitance and any external capacitor on the gate.

This has to be positive, right?

And this to be fairly large, right, as peak current is concerned?

Could anyone help to enlighten me? Thank you.

Dyu