cupoftea

Advanced Member level 5

Hi,

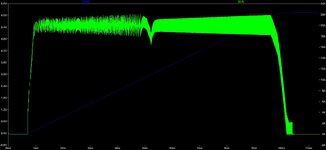

We are doing a Buck supercap charger, repeatedly charging 25F from 0 to 6V, from 37Vin.

Obviously, the Buck controller should ideally work in constant off time mode till the supercap gets above 1V, otherwise the duty cycle , and on_time , is ridiculously small.

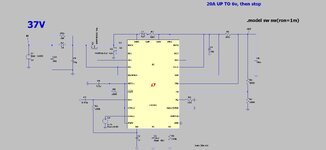

But there is nothing on the market for this application. The best we can find is the LM5117 which uses ECM, so can at least handle low on times without spurious turning off from the switch-on spike.

Why is this application so underserved?

LM5117

We are doing a Buck supercap charger, repeatedly charging 25F from 0 to 6V, from 37Vin.

Obviously, the Buck controller should ideally work in constant off time mode till the supercap gets above 1V, otherwise the duty cycle , and on_time , is ridiculously small.

But there is nothing on the market for this application. The best we can find is the LM5117 which uses ECM, so can at least handle low on times without spurious turning off from the switch-on spike.

Why is this application so underserved?

LM5117