cmos_ajay

Full Member level 2

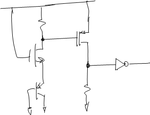

Hello, I need to design a power on reset circuit that consumes only 0.7 micro ampere. Supply voltage VDD can range from 1.4V and above. When the supply is rising and it reaches say 1.2V, the POR signal should go high. Can you suggest any robust architecture for this ? Any schematic or technical document will be of great help. Thanks .