ctzof

Full Member level 3

Hello,

I am rather new to FPGA design and I am having some difficulties with a design. Here is the problem:

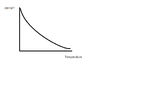

I want to build a look up table to generate the outputs of a specific function. So I have a temperature sensor and depending on the measured temperature I want to produce an offset which is going to be add to the output signal. The offset is straightforward and follows a specific line. The temperature value is a 10-bit unsigned integer which means that is going to produce 1024 different values-offsets. Its value in the look up table is 10-bit which means that I need a space of 1024x10 =10 kbit. The thing is that I want to use the same look up table many times in my project and I am rather limited in terms of resources. What I was thinking is to use less points than 1024 and some how compute the output value when the input value is somewhere in between (I am not really sure but I think this term called linear interpolation). Is there a possible way to do that in an FPGA any ideas?

My computations are made with unsigned numbers.

I am rather new to FPGA design and I am having some difficulties with a design. Here is the problem:

I want to build a look up table to generate the outputs of a specific function. So I have a temperature sensor and depending on the measured temperature I want to produce an offset which is going to be add to the output signal. The offset is straightforward and follows a specific line. The temperature value is a 10-bit unsigned integer which means that is going to produce 1024 different values-offsets. Its value in the look up table is 10-bit which means that I need a space of 1024x10 =10 kbit. The thing is that I want to use the same look up table many times in my project and I am rather limited in terms of resources. What I was thinking is to use less points than 1024 and some how compute the output value when the input value is somewhere in between (I am not really sure but I think this term called linear interpolation). Is there a possible way to do that in an FPGA any ideas?

My computations are made with unsigned numbers.