cupoftea

Advanced Member level 5

Hi,

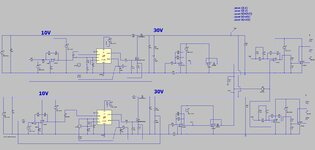

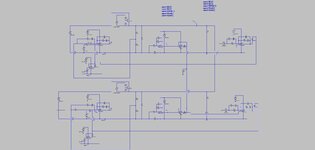

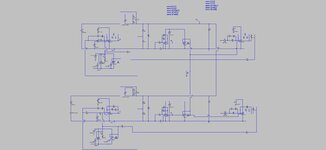

The attached shows load sharing boost converters. Though, Instead of sharing simultaneously, they swap the load between themselves repeatedly.

Do you know how to solve this?

Should one converter "always" be the master, instead of as shown, where either can be master.

(LTspice and jpeg attached)

The operation just passes the amplified output current sense value to the joint "share" bus, and each converter trys to get equal to that in its current delivery (kind of like the UC3902 does it)

The attached shows load sharing boost converters. Though, Instead of sharing simultaneously, they swap the load between themselves repeatedly.

Do you know how to solve this?

Should one converter "always" be the master, instead of as shown, where either can be master.

(LTspice and jpeg attached)

The operation just passes the amplified output current sense value to the joint "share" bus, and each converter trys to get equal to that in its current delivery (kind of like the UC3902 does it)