crossflow

Newbie

Hi all,

I'm trying to design a digitally buck controller with a direct form I IIR filter in a fixed-point representation, it works but I see small limit cycles.

Vin is 12V and Vout 3.3V, buck complex conjugate poles are at 15kHz and bandwidth and switching frequency is 1MHz.

I'm using type III regulation, 3 poles and 3 zero. First pole is at 500Hz, second and third poles at half switching frequency.

To boost phase shift I placed 2 zero at resonant frequency of buck, cross over frequency is fixed at 90kHz, resulting in a dc gain of 25dB

Sample frequency is 1MHz too, dpwm and compensator clock are synchronous with switching period.

Z-transform equation coefficients are scaled up by a factor of 2^16.

Adc resolution is 8 bit and input dynamic is windowed in 1V around target voltage.

Dpwm resolution is 14 bit and 5 bit of Vin feed forward Adc are added to the duty word.

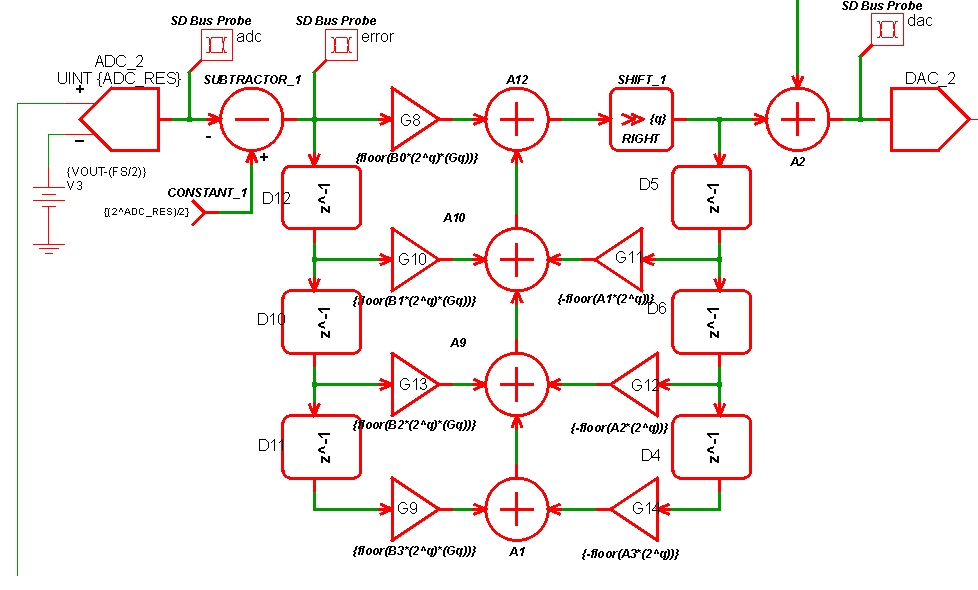

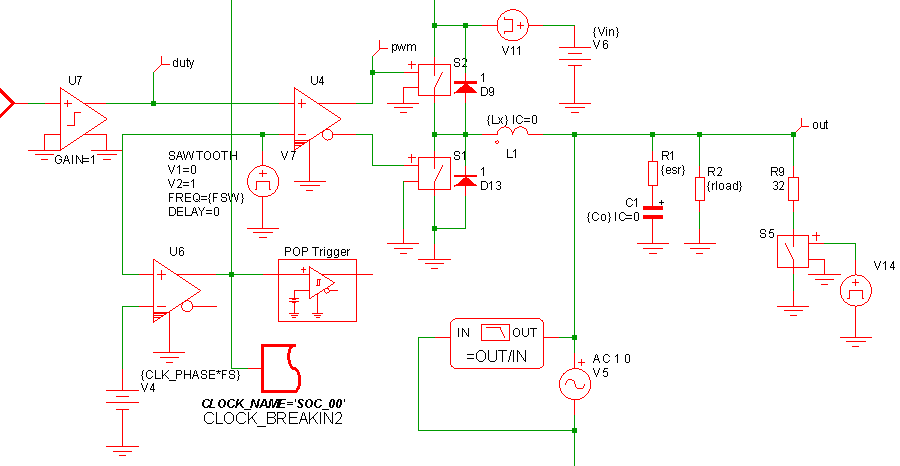

Here you can see simplis schematic and waveforms

compensator

modulator and filter:

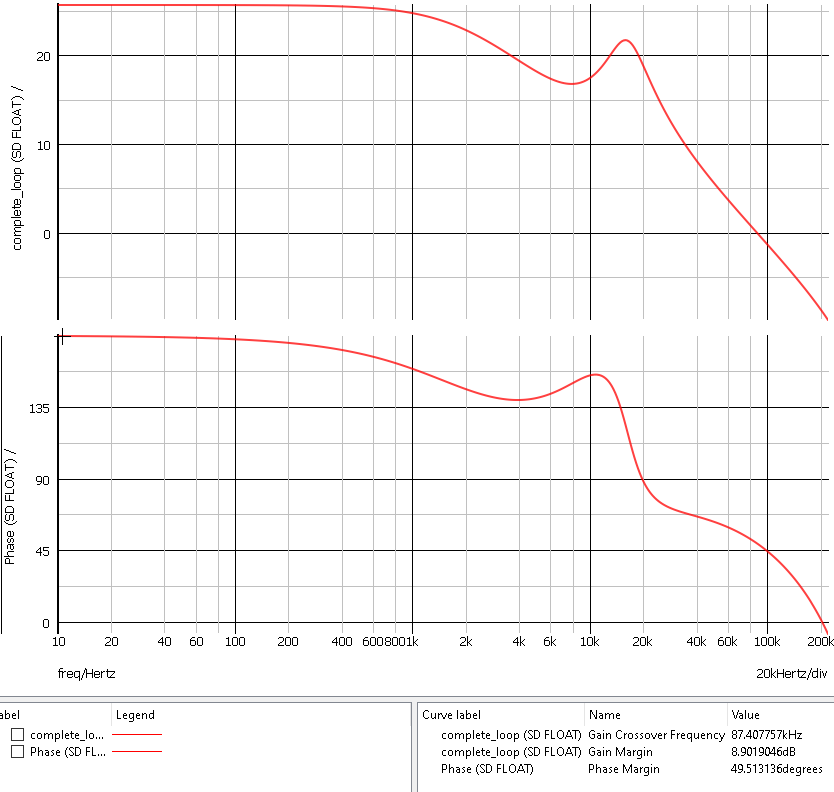

AC simulation of loop gain in double precision resolution (no quantization modeled):

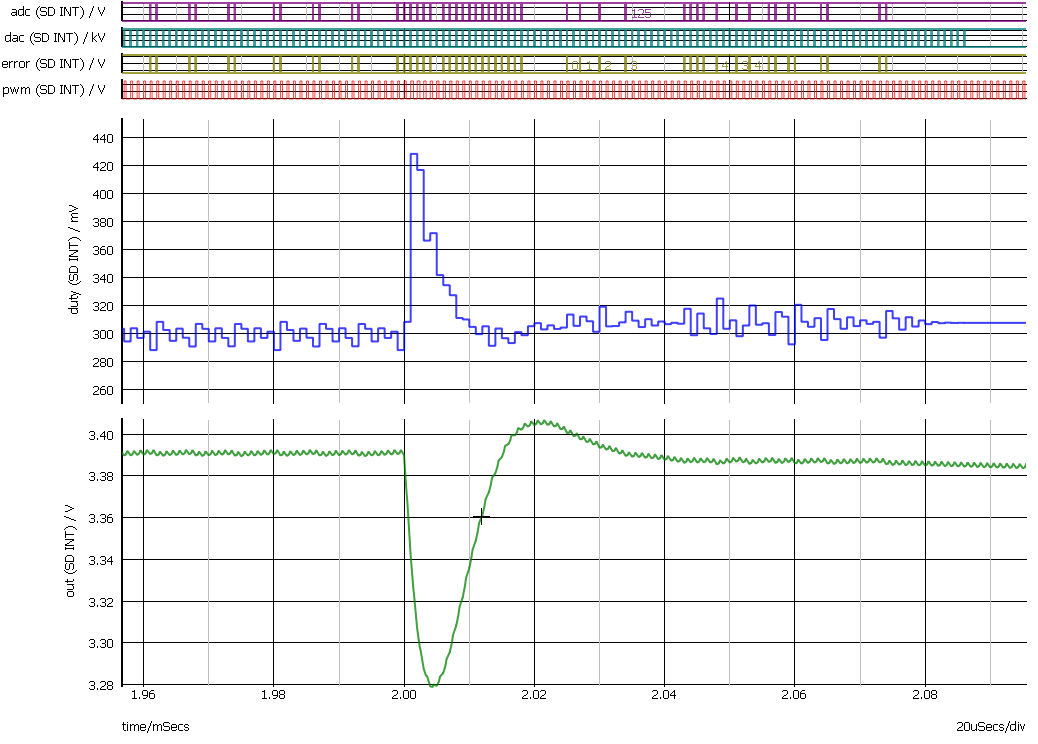

load step transient simulation considering quantization:

As you can see duty word is oscillating with periodic function and output voltage is perturbed consequently.

Curiously compensator is oscillating even when ADC is not

Adc levels are larger than dpwm levels so at least the most important condition to avoid limit cycles is respected.

I know that there are other conditions but I don't know which ones.

Could it be some a quantization noise problem?

Please could you help me to understand why these oscillations occur and explain how to eliminate them?

Thank you very much.

I'm trying to design a digitally buck controller with a direct form I IIR filter in a fixed-point representation, it works but I see small limit cycles.

Vin is 12V and Vout 3.3V, buck complex conjugate poles are at 15kHz and bandwidth and switching frequency is 1MHz.

I'm using type III regulation, 3 poles and 3 zero. First pole is at 500Hz, second and third poles at half switching frequency.

To boost phase shift I placed 2 zero at resonant frequency of buck, cross over frequency is fixed at 90kHz, resulting in a dc gain of 25dB

Sample frequency is 1MHz too, dpwm and compensator clock are synchronous with switching period.

Z-transform equation coefficients are scaled up by a factor of 2^16.

Adc resolution is 8 bit and input dynamic is windowed in 1V around target voltage.

Dpwm resolution is 14 bit and 5 bit of Vin feed forward Adc are added to the duty word.

Here you can see simplis schematic and waveforms

compensator

modulator and filter:

AC simulation of loop gain in double precision resolution (no quantization modeled):

load step transient simulation considering quantization:

As you can see duty word is oscillating with periodic function and output voltage is perturbed consequently.

Curiously compensator is oscillating even when ADC is not

Adc levels are larger than dpwm levels so at least the most important condition to avoid limit cycles is respected.

I know that there are other conditions but I don't know which ones.

Could it be some a quantization noise problem?

Please could you help me to understand why these oscillations occur and explain how to eliminate them?

Thank you very much.