kingearlkwan

Junior Member level 1

- Joined

- Apr 26, 2013

- Messages

- 15

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,393

Hi Guys,

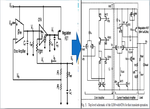

Need some help understanding the circuit attached. The circuit utilizes an OTA error amplifier with current fb amp to improved transient response. Can anyone help me explain in details how the ckt behaves specially on the transistor levels when it encounters a current load variations?

Thanks!

Need some help understanding the circuit attached. The circuit utilizes an OTA error amplifier with current fb amp to improved transient response. Can anyone help me explain in details how the ckt behaves specially on the transistor levels when it encounters a current load variations?

Thanks!