vidyaredy

Member level 2

xilinx delay cell

Hi friends,

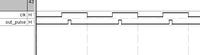

In my design I will be delaying one signal(clock) to generate other signals. I have used xilinx primitives buffer(buf or bufg) to generate delay elements. When I synthesize this individually it gives 7.266ns combinational path delay. when I instantiated this in top module 15 times its generating the same delay......... :-( . Also sythesis report says the destination library for buf or bufg has different definition the model has been changed to buf1 or bufg1. when I simulated in modelsim all outputs are happenning on the same edge even though the design is not synchronised with clock. I am not able to see delay in signals at all.....plz let me know if u have any idea.

Hi friends,

In my design I will be delaying one signal(clock) to generate other signals. I have used xilinx primitives buffer(buf or bufg) to generate delay elements. When I synthesize this individually it gives 7.266ns combinational path delay. when I instantiated this in top module 15 times its generating the same delay......... :-( . Also sythesis report says the destination library for buf or bufg has different definition the model has been changed to buf1 or bufg1. when I simulated in modelsim all outputs are happenning on the same edge even though the design is not synchronised with clock. I am not able to see delay in signals at all.....plz let me know if u have any idea.