sabu31

Advanced Member level 1

Dear All,

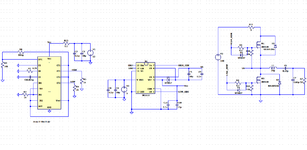

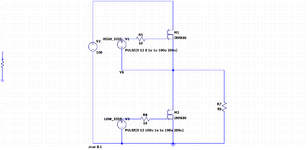

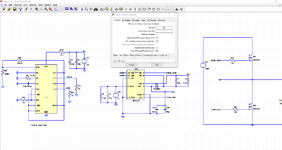

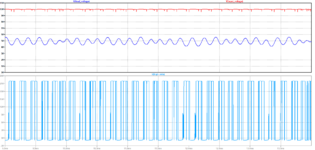

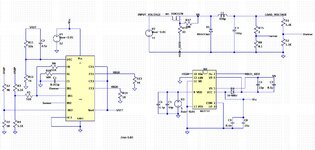

I am trying to simulate an H-Bridge circuit using LTSPICE using IR2110 as a MOSFET driver. However, I am facing an issue with the simulation. It says the simulation step size is too small. Trouble with IRF830 m-1 instance. I am attaching the circuit for your reference. Please let me know what should be done to rectify this issue.

Thanking you.

I am trying to simulate an H-Bridge circuit using LTSPICE using IR2110 as a MOSFET driver. However, I am facing an issue with the simulation. It says the simulation step size is too small. Trouble with IRF830 m-1 instance. I am attaching the circuit for your reference. Please let me know what should be done to rectify this issue.

Thanking you.