yefj

Advanced Member level 4

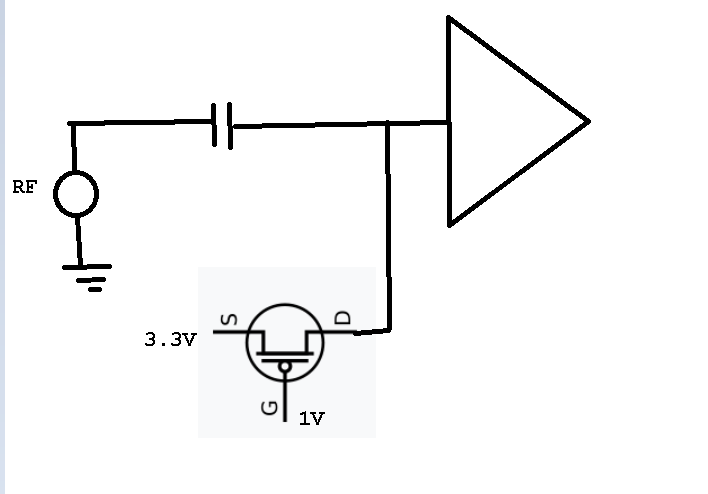

Hello i have a configuration as shown bellow which i dont understand its logic:

This circuit is supposed to pass 3.3V to the amplifier.

I dont have any knowledge about the drain in the mosfet.

What is the drain voltage in this case, how can i see if the transistor is saturated or not?

This circuit is supposed to pass 3.3V to the amplifier.

I dont have any knowledge about the drain in the mosfet.

What is the drain voltage in this case, how can i see if the transistor is saturated or not?