iammituraj

Newbie

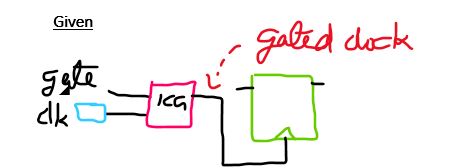

I have a negative latch based IGC like this in clock path which takes care of glitch on switching gate.

'gate' is coming from another clock domain sysclk. All clocks (clk, sysclk) are defined in SDC. Do I have to add any additional constraints here like clock gating check? I have a feeling whether I have to create a generated clock at the output of IGC.

'gate' is coming from another clock domain sysclk. All clocks (clk, sysclk) are defined in SDC. Do I have to add any additional constraints here like clock gating check? I have a feeling whether I have to create a generated clock at the output of IGC.