pYrana13

Junior Member level 1

Hi all,

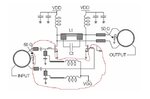

I came across this RF class-D power amplifier design and want to know, what type of input matching has been used here? I cant really understand the input matching schematic below(shown in the red region). Is it only for matching purpose or is there any other purpose? Could someone please explain it to me?

Thanks a lot.

I came across this RF class-D power amplifier design and want to know, what type of input matching has been used here? I cant really understand the input matching schematic below(shown in the red region). Is it only for matching purpose or is there any other purpose? Could someone please explain it to me?

Thanks a lot.