mordak

Member level 5

- Joined

- Mar 8, 2013

- Messages

- 82

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Location

- Neverland

- Activity points

- 2,134

Hi,

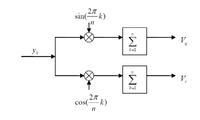

I have a question about extracting in-phase and quadrature (IQ) components of a signal. If we have an analog signal with frequency Fin, and want to use a system like the one in the attached picture, while Yk is the output of an ADC

I was wondering whether there should be any relation between sampling frequency of the ADC and the input signal frequency in order to be able to extract IQ or not.

Thanks!

I have a question about extracting in-phase and quadrature (IQ) components of a signal. If we have an analog signal with frequency Fin, and want to use a system like the one in the attached picture, while Yk is the output of an ADC

I was wondering whether there should be any relation between sampling frequency of the ADC and the input signal frequency in order to be able to extract IQ or not.

Thanks!