Powerfreak

Newbie level 3

Please find some answers to your remarks.

[...]

Optocouplers are far away from the IGBT's so gate rails are also long [...]

###Please try to use drilles wires instead, 2drilles wires per IGBT.

[...]

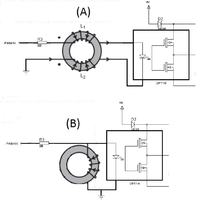

Do you suggest me to change only layout or both layout and IGBT drivers? I choosed those drivers as they are easy to apply and does both drive and isolation. If I use a common gate driver IC, I also need to use pulse transformer in order to do the isolation between microcontroller and power levels.

###first lets find the weak point, currently we have too less details

[...]

I don't use ceramic but I think they are polyester through hole capacitors both at Vcc and 15V supply rails.

###Polyester is fine for the moment

I think I don't have dead time issues. The time delay between signals are enough and nothing changes when I increase and decrease the dead time ofcourse between safe area (I apply at least 240ns at most 1us)

IGBT's and gate drivers are both really fast. I choosed them intentionally that fast to do the switching fast and get rid of much switching loss. I think 1..3us switching time is too slow for this IGBTs and would lead to much switching loss. I think gate signal path is too long. I hope I could overcome them with new layout.

###right, but please DO try reducing the switching speed with less current to make sure that this is not the issue. To close this topic finally please start with app 4R7Ohm as gate resistor, continue with 10R, 15R, 22R. 47R. 100R. 150R. 220R and do measure and compare the length of the oscillation and the 200ns "hills" in the switching processes which can be seen on the 2 upper pictures.

Than add a 220µf Elko to each Driver, make sure that the polyester is changed to a 2µ2..4µ7 Kerko with shortest wires to the driver directly and compare with 2..3 Resistor values.

Than add >33mF consisting out of 5..10 paralleled Electrolytics which are mounted with max 5cm thick wire over the H-bridge and tell us the difference in switching and disturbance

This above will help to reduce the possible issues...

I am very curious to your results

[...]

Optocouplers are far away from the IGBT's so gate rails are also long [...]

###Please try to use drilles wires instead, 2drilles wires per IGBT.

[...]

Do you suggest me to change only layout or both layout and IGBT drivers? I choosed those drivers as they are easy to apply and does both drive and isolation. If I use a common gate driver IC, I also need to use pulse transformer in order to do the isolation between microcontroller and power levels.

###first lets find the weak point, currently we have too less details

[...]

I don't use ceramic but I think they are polyester through hole capacitors both at Vcc and 15V supply rails.

###Polyester is fine for the moment

I think I don't have dead time issues. The time delay between signals are enough and nothing changes when I increase and decrease the dead time ofcourse between safe area (I apply at least 240ns at most 1us)

IGBT's and gate drivers are both really fast. I choosed them intentionally that fast to do the switching fast and get rid of much switching loss. I think 1..3us switching time is too slow for this IGBTs and would lead to much switching loss. I think gate signal path is too long. I hope I could overcome them with new layout.

###right, but please DO try reducing the switching speed with less current to make sure that this is not the issue. To close this topic finally please start with app 4R7Ohm as gate resistor, continue with 10R, 15R, 22R. 47R. 100R. 150R. 220R and do measure and compare the length of the oscillation and the 200ns "hills" in the switching processes which can be seen on the 2 upper pictures.

Than add a 220µf Elko to each Driver, make sure that the polyester is changed to a 2µ2..4µ7 Kerko with shortest wires to the driver directly and compare with 2..3 Resistor values.

Than add >33mF consisting out of 5..10 paralleled Electrolytics which are mounted with max 5cm thick wire over the H-bridge and tell us the difference in switching and disturbance

This above will help to reduce the possible issues...

I am very curious to your results