vaah

Member level 3

Hello,

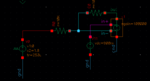

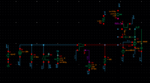

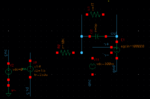

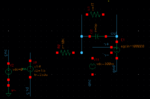

I would like to build an ideal integrator in Cadence. Currently, I am using "VCVS" as an amplifier shown in the fig

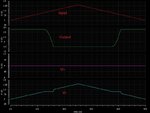

When I simulate the circuit, apparently, capacitor feedback does not work properly. The opamp model acts like a comparator. As long as negative input has a larger voltage output shows the minimum voltage and Vice versa. I am wondering if someone might have the same problem. I appreciate it if you could let me know how to resolve the issue!

Do you have any suggestion how to model an ideal integrator in Cadence? Preferably, I do not want to use Verilog-A opamp.

Thanks.

I would like to build an ideal integrator in Cadence. Currently, I am using "VCVS" as an amplifier shown in the fig

When I simulate the circuit, apparently, capacitor feedback does not work properly. The opamp model acts like a comparator. As long as negative input has a larger voltage output shows the minimum voltage and Vice versa. I am wondering if someone might have the same problem. I appreciate it if you could let me know how to resolve the issue!

Do you have any suggestion how to model an ideal integrator in Cadence? Preferably, I do not want to use Verilog-A opamp.

Thanks.