dor8

Junior Member level 1

I have a problem with my circle that the drivers are burned (pin 4 shorter to pin 2) or the drivers are not working properly (HO takes out constant signal regardless of to his entry).

I use in UCC27200 driver.

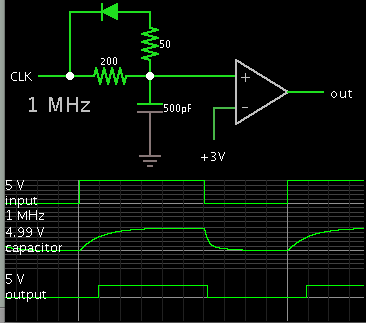

Can some of the problems were caused because I don’t have delay time between switching of the transistors ,So I want to create a circle of delay (Figure 2).

My goal is to create a time delay of a 100n but I need help in calculating the components that would give me the time delay.

And generally how I calculated delay tie in RC Circle?

I use in UCC27200 driver.

Can some of the problems were caused because I don’t have delay time between switching of the transistors ,So I want to create a circle of delay (Figure 2).

My goal is to create a time delay of a 100n but I need help in calculating the components that would give me the time delay.

And generally how I calculated delay tie in RC Circle?